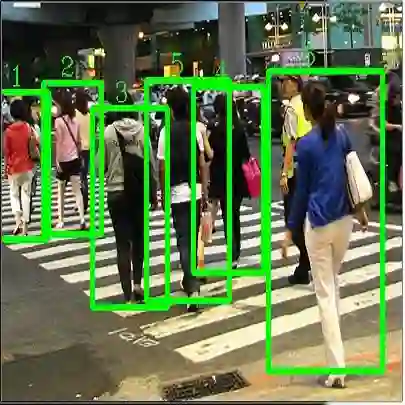

Spiking neural networks (SNNs), which are inspired by the human brain, have recently gained popularity due to their relatively simple and low-power hardware for transmitting binary spikes and highly sparse activation maps. However, because SNNs contain extra time dimension information, the SNN accelerator will require more buffers and take longer to infer, especially for the more difficult high-resolution object detection task. As a result, this paper proposes a sparse compressed spiking neural network accelerator that takes advantage of the high sparsity of activation maps and weights by utilizing the proposed gated one-to-all product for low power and highly parallel model execution. The experimental result of the neural network shows 71.5$\%$ mAP with mixed (1,3) time steps on the IVS 3cls dataset. The accelerator with the TSMC 28nm CMOS process can achieve 1024$\times$576@29 frames per second processing when running at 500MHz with 35.88TOPS/W energy efficiency and 1.05mJ energy consumption per frame.

翻译:受人类大脑启发的Spik神经网络(SNNS)最近由于相对简单和低功率的硬件来传送二进制钉钉和高度分散的激活地图而变得受欢迎,然而,由于SNN的加速器包含额外的时间维度信息,因此需要更多的缓冲器和较长的推导时间,特别是较困难的高分辨率物体探测任务。因此,本文件提议利用激活图和重量的高度宽度,利用拟议的一对一门产品,用于低功率和高度平行的模型执行。神经网络的实验结果显示,在IVS 3cls数据集上,有71.5 $ mAP的混合时间(1,3)级。TSMC 28nm CMOS进程的加速器每第二次处理可达到1024美元,576@29框架,当时在500兆赫兹运行时达到35.88TOPS/W的能源效率和1.05米J的能量消耗率。