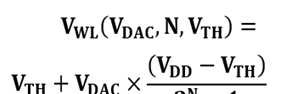

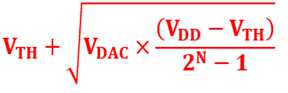

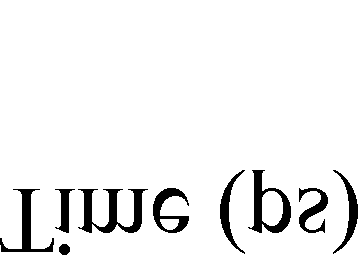

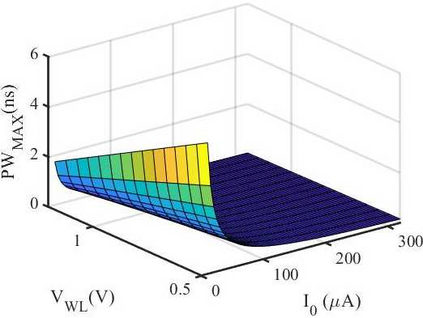

This paper presents a novel circuit (AID) to improve the accuracy of an energy-efficient in-memory multiplier using a standard 6T-SRAM. The state-of-the-art discharge-based in-SRAM multiplication accelerators suffer from a non-linear behavior in their bit-line (BL, BLB) due to the quadratic nature of the access transistor that leads to a poor signal-to-noise ratio (SNR). In order to achieve linearity in the BLB voltage, we propose a novel root function technique on the access transistor's gate that results in accuracy improvement of on average 10.77 dB SNR compared to state-of-the-art discharge-based topologies. Our analytical methods and a circuit simulation in a 65 nm CMOS technology verify that the proposed technique consumes 0.523 pJ per computation (multiplication, accumulation, and preset) from a power supply of 1V, which is 51.18% lower compared to other state-of-the-art techniques. We have performed an extensive Monte Carlo based simulation for a 4x4 multiplication operation, and our novel technique presents less than 0.086 standard deviations for the worst-case incorrect output scenario.

翻译:本文展示了一种新的电路(AID),用标准的 6T-SRAM 来提高高能效的模拟乘数的准确性。在SRAM 中,最先进的基于排放的加速器在比线(BL, BLB)中出现非线性行为(BL, BLB),原因是进入晶体管的四边形性质导致信号对噪音比率差(SNR)。为了实现BLB电压的线性,我们提议在存取晶体管门上采用一种新的根功能技术,使平均10.77 dB SNR 与基于排放的状态的表层相比,其精确性得到提高。我们的分析方法和65 nm CMOS 技术的电路模拟证实,拟议的技术从1V的电力供应量(倍增、累积和预设)中,每计算0.523 pJ,比其他先进技术低51.18%。我们为4x新式的不精确模型进行了广泛的蒙特-卡洛最差的模拟。