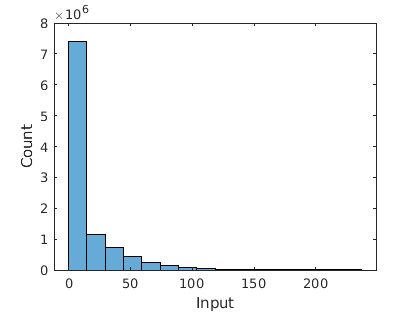

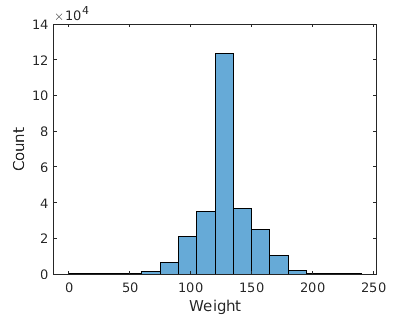

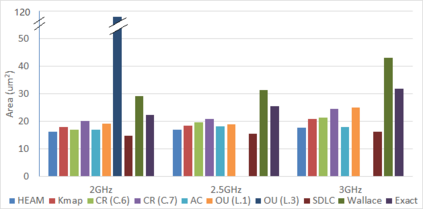

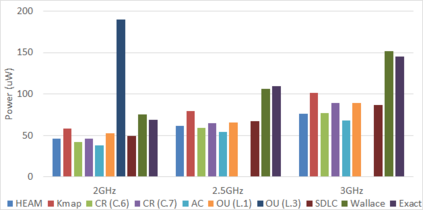

We propose an optimization method for the automatic design of approximate multipliers, which minimizes the average error according to the operand distributions. Our multiplier achieves up to 50.24% higher accuracy than the best reproduced approximate multiplier in DNNs, with 15.76% smaller area, 25.05% less power consumption, and 3.50% shorter delay. Compared with an exact multiplier, our multiplier reduces the area, power consumption, and delay by 44.94%, 47.63%, and 16.78%, respectively, with negligible accuracy losses. The tested DNN accelerator modules with our multiplier obtain up to 18.70% smaller area and 9.99% less power consumption than the original modules.

翻译:我们建议了一种最优化的近似乘数自动设计方法,根据功能分布,这可以将平均差错最小化。 我们的乘数比DNNs中最佳复制近似乘数的精确度高出50.24%,其面积小15.76%,电耗少25.05%,延迟率短3.50%。 与精确乘数相比,我们的乘数将面积、电耗和延迟率分别减少44.94%、47.63%和16.78%,其精确度损失微乎其微。 测试的DNN加速器模块与我们的倍数相比,其面积小到18.70%,电耗少9.99%。