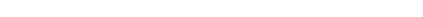

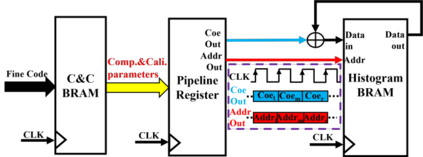

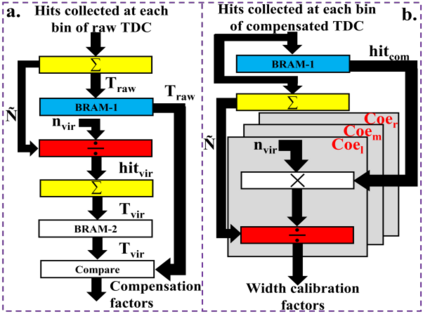

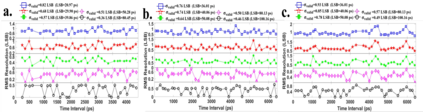

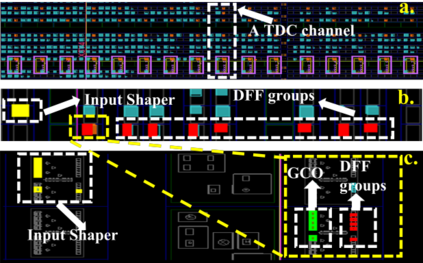

This paper presents a low hardware consumption, resolution-configurable, automatically calibrating Gray code oscillator time-to-digital converter (TDC) in Xilinx 16nm UltraScale+, 20nm UltraScale and 28nm Virtex-7 field-programmable gate arrays (FPGAs). The proposed TDC has several innovations: 1) a sampling matrix to improve the resolution. 2) a virtual bin calibration method (VBCM) to realize resolution configuration and automatic calibration. 3) a hardware implementation of the VBCM in standard FPGA devices. We implemented and evaluated a 16-channel TDC system in all three FPGAs. The UltraScale+ version achieved the best resolution (least significant bit, LSB) of 20.97 ps with 0.09 LSB averaged peak-peak differential linearity (DNLpk-pk). The UltraScale and Virtex-7 versions achieved the best resolutions of 36.01 ps with 0.10 LSB averaged DNLpk-pk and 34.84 ps with 0.08 LSB averaged DNLpk-pk, respectively.

翻译:本文介绍了在Xilinx 16nm Ultrasultation+, 20nm Ultrasult 和 28nm Virtex-7 实地可编程门阵列(FPGAs)中低硬件消耗量、分辨率可配置、自动校准灰分码振荡器时间转换器(TDC),拟议的TDC有几项创新:(1) 改进分辨率的抽样矩阵;(2) 实现分辨率配置和自动校准的虚拟箱校准方法(VBCM) 3) 标准FPGA装置中VBCM的硬件实施。我们在所有3个FPGAs中实施并评价了16个通道的TDC系统。Ultrasulation+ 实现了20.97 ps的最佳分辨率(最小点,LSB),达到20.09 LSB平均峰峰点差线(DNLpk-pk); 超标准和Virtex-7 版本实现了36.01 ps最佳分辨率(0.10 LSBd DNpk-pkpk-pk)和34.84 ps,分别达到0.08LSBs。