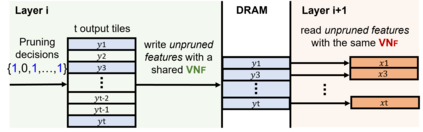

This paper introduces MGX, a near-zero overhead memory protection scheme for hardware accelerators. MGX minimizes the performance overhead of off-chip memory encryption and integrity verification by exploiting the application-specific properties of the accelerator execution. In particular, accelerators tend to explicitly manage data movement between on-chip and off-chip memories. Therefore, the general memory access pattern of an accelerator can largely be determined for a given application. Exploiting these characteristics, MGX generates version numbers used in memory encryption and integrity verification using on-chip accelerator state rather than storing them in the off-chip memory; it also customizes the granularity of the memory protection to match the granularity used by the accelerator. To demonstrate the efficacy of MGX, we present an in-depth study of MGX for DNN and graph algorithms. Experimental results show that on average, MGX lowers the performance overhead of memory protection from 28% and 33% to 4% and 5% for DNN and graph processing accelerators in a wide range of benchmarks, respectively.

翻译:本文引入了 MGX, 这是用于硬件加速器的近零顶存储保护机制。 MGX 通过利用加速器执行的应用程序特性, 最小化了离芯内存加密和完整性核查的性能管理。 特别是, 加速器往往明确管理在芯片上和离芯存储器记忆之间的数据移动。 因此, 加速器的一般存取模式可以在很大程度上为特定应用程序确定。 利用这些特性, MGX 生成了用于在芯片加速器状态上进行记忆加密和完整性核查的版本号, 而不是将其储存在离芯存储器内; 它还定制了记忆保护的颗粒性, 以匹配加速器所使用的颗粒性。 为了显示 MGX 的功效, 我们为 DNN 和 图形算法对MGX 进行一项深入的研究。 实验结果表明, 平均而言, MGX 将记忆保护的性能管理器的运行量从28% 和 33% 降至 4% 和 5% 。 DNNN 和 图表 分别处理一个宽基准 的磁带 。