随着后摩尔时代的来临,现场可编程门阵列(FPGA)凭借其灵活的重复可编程特性、开发成本低的特点,现已被广泛应用于物联网 (IoTs)、5G通信、航空航天以及武器装备等各个领域。作为FPGA设计开发过程中所必备的手段,FPGA电子设计自动化(EDA)技术的研究在各界得到了广泛的关注。尤其是在机器学习方法的推动下,FPGA EDA工具的运行效率和结果质量(QoR)得到了很大的提升。该文首先对FPGA EDA技术与机器学习技术的概念内涵进行了简要概述,随后综述了机器学习技术在FPGA EDA高层次综合(HLS)、逻辑综合、布局与布线等各个不同阶段应用的研究现状。最后,对基于机器学习的FPGA EDA技术的发展进行了展望。以期为本领域及相关领域的专家和学者提供参考,为后摩尔时代我国集成电路产业的发展提供技术支持。

1. 引言

随着硅工艺发展接近物理极限,用来刻画工艺演进速度的摩尔定律也开始被打破,半导体行业迎来了后摩尔时代[1,2]。然而集成电路芯片产业并没有因此而停滞发展,现场可编程门阵列(Field Programmable Gate Array, FPGA)由于所具有的高度灵活、可定制以及支持高并发等特性[3],被广泛应用于后摩尔时代的各个领域[4-8]。与此同时,为了能够适应更加复杂的电路系统,FPGA芯片的集成度也在不断增大,从最初只包含有几千个逻辑门的单功能芯片发展到了现今集成了数据信号处理(Digital Signal Processing, DSP)单元、块随机存取存储器(Block Random Access Memory, BRAM)以及多核微处理器的片上系统,FPGA芯片的集成度增加了数万倍。如此高的芯片集成度使得手动进行电路设计已经不现实,开发设计人员更加依赖于电子设计自动化(Electronic Design Automation, EDA)工具对FPGA数字集成电路进行设计[9,10]。但随着FPGA芯片规模的不断增大以及片上设计复杂度的不断提升,例如,AMD Xilinx发布的Virtex UltraScale+VU19P FPGA,其包含900万个逻辑单元以及近350亿个晶体管,而Intel发布的Stratix 10 GX 10M FPGA,更是包含了1020万个逻辑单元以及近430亿个晶体管,对FPGA EDA工具的可扩展性和工作效率提出了严峻的挑战[11,12],即便FPGA的可重复编程特性允许硬件设计的快速实现以及系统内调试,从而能够提高工作设计人员的工作效率,但如果EDA工具的运行时间过长或结果质量(Quality of Result, QoR)很差,这一优势就会被明显削弱。因此,FPGA EDA算法和软件工具亟需朝着更加高效、智能的方向进行演进[13]。

如今,机器学习在我们的生活中发挥着越来越重要的作用,已经在许多场景中得到了广泛的应用。机器学习方法在解决分类、检测和设计空间探索问题等方面展现了令人惊叹的性能[14]。此外,机器学习方法也显现出为许多非确定性多项式(Non-deterministic Polynomial, NP)完全问题生成高质量解决方案的巨大潜力,这些NP完全问题在FPGA EDA领域是非常常见的,而传统的解决方案常常由于缺乏知识积累,需要耗费大量的时间和资源从头解决所有问题[15]。相对应的,机器学习方法专注于提取可以在其他相关和类似情况下重用的高级特征或模型,避免重复的复杂分析。因此,应用机器学习方法是加速解决FPGA EDA问题的一个重要研究方向[13,16]。

可喜的是,国内外学者针对基于机器学习方法的FPGA EDA技术的研究已经取得了具有前瞻性的研究成果和进展。本文分析梳理了近年来应用机器学习解决FPGA EDA中一些关键问题的研究成果,对FPGA EDA和机器学习的背景知识进行了简要概述,调研了机器学习在FPGA EDA流程不同阶段应用的研究现状,即HLS、逻辑综合、布局以及布线,在此基础上对机器学习未来在FPGA EDA技术中的应用进行了展望。

2. FPGA EDA与机器学习技术概述

**2.1 FPGA EDA技术概述

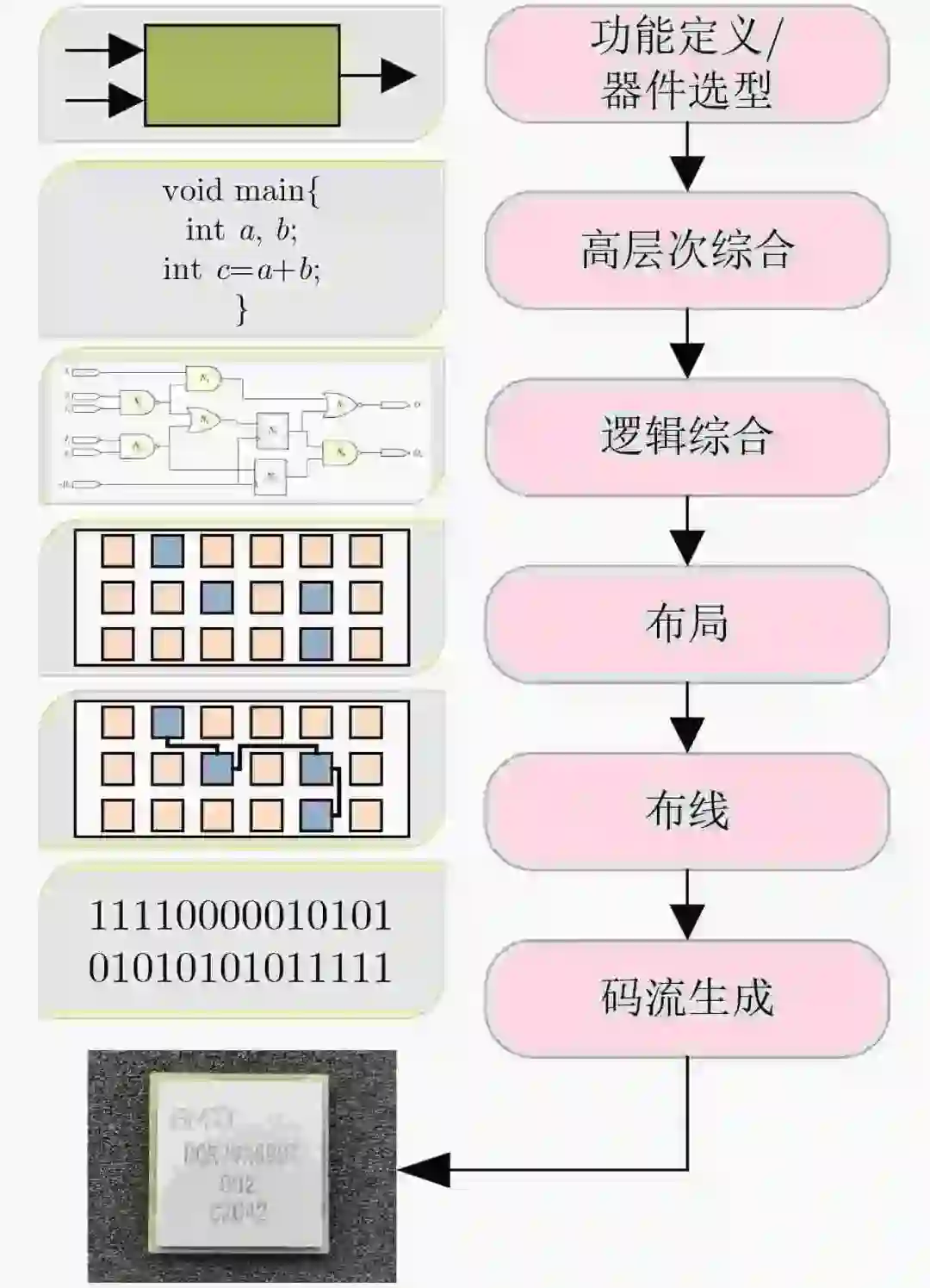

作为FPGA芯片设计、应用过程中不可或缺的重要组成部分,在过去的30余年中,FPGA EDA的设计流程变得越来越规范且复杂,具体包括高层次综合(High Level Synthesis, HLS)、逻辑综合、布局、布线以及码流生成[17,18],如图1所示。

FPGA EDA基本流程HLS是指将高层次语言描述的逻辑结构自动转换成低抽象级语言描述的电路模型的过程,即HLS能够将C、C++、SystemC等具有较高的抽象度且不具备时钟或时序概念的高层次语言自动转化为Verilog、VHDL、SystemVerilog等低层次语言[ 19,20]。由于Verilog、VHDL、SystemVerilog能够用来描述时钟周期精确的寄存器传输级(Register Transfer Level, RTL)电路模型,是当前FPGA设计中最为普遍适用的电路建模与描述方式。HLS技术的应用可以提高设计速度、缩短设计周期,方便设计者在系统级进行设计方案的探索、在算法级对设计进行优化。

逻辑综合能够将HDL文件转换为描述指定FPGA器件上不同逻辑单元连接关系的网表文件,需要指出的是,网表中的连接关系只是逻辑连接,即逻辑综合工具只是给出了所需实现的设计的一个“草图”,这个“草图”最终需要由FPGA芯片中可用的逻辑资源来实现[21]。逻辑综合是一个非常复杂的过程,通常情形下只能通过启发式方法来得到一个次优的解决方案。

布局是指在一定的约束条件下(例如,线长、时延、功耗以及面积等),将逻辑综合过程得到的电路网表中的逻辑单元与实际FPGA芯片中的物理位置建立一对一映射的过程[22]。布局作为FPGA EDA流程中的关键环节,同时也是FPGA编译过程中最耗时的步骤之一。由于FPGA中的布线资源都是预置的且容量有限,一旦布局算法的解需要过多的布线资源,后续的布线过程将会失败或是需要很长的时间才会得到一个可行的布线解决方案,因此,一个好的布局解决方案对于FPGA EDA的工作流程至关重要。

布线能够在保证资源合法使用的前提下,通过配置FPGA芯片中的可编程开关,从而通过利用硬连线资源连通电路线网中所有的逻辑连接。与此同时,为了保证最终在FPGA芯片实现后的电路设计中的逻辑信号的正常传输,不同线网间的逻辑连接不能够共享相同的硬连线资源[23]。

执行完布线操作后,便可以生成二进制的码流文件,将其下载到芯片内部,最终完成FPGA的配置流程。 得益于学术界和工业界30余年的努力,FPGA芯片的设计流程得到了很好的发展。然而,随着FPGA芯片规模的不断增长,亟需引入更加高效的设计方法来降低设计成本、提升设计效率以及QoR。近年来,机器学习技术的飞速发展为解决上述问题提供了一个全新的视角。本文综述了机器学习技术在FPGA EDA HLS、逻辑综合、布局、布线等流程中的应用情况,并对发展趋势进行了总结,希冀为未来FPGA EDA技术的发展起到一定促进作用。

**2.2 机器学习技术概述

机器学习技术是一种能够自动从数据集或是先验知识中提取有用信息的技术,通常情形下,基于机器学习技术的解决方案按照学习范式的不同可以分为监督学习、无监督学习、主动学习以及强化学习等几种类型[24,25]。监督学习与无监督学习的区别在于机器学习模型的输入数据事先是否被标记,通过监督学习或无监督学习,机器学习模型首先通过离线的方式在静态的数据集上进行训练,在模型的训练误差满足要求后,便可以用于在线部署。在利用一些传统的监督学习方法进行分类训练时,数据样本的规模越大,分类的效果便越好。但在实际的应用场景中,标记样本的获取往往是十分困难的,大多数情况下需要各领域的专家通过手工的方式进行标注,所耗费的时间成本和经济成本是无法负担的。为了降低数据标记过程所耗费的成本,进而能够使用较少的训练样本来获得性能较好的机器学习模型,主动学习的概念应运而生。主动学习是指机器学习模型能够从输入空间中查询得到最有用的未标记的样本,并交由专家进行标记,随后再利用上述已标记的样本来训练机器学习模型以提高模型的精确度,这样便能够降低海量数据标记所带来的成本浪费的问题。最后便是强化学习,强化学习事先不要求给定任何数据,强调决策体(Agent)如何通过采取行动(Action)-获取奖励(Award)的方式与环境(Environment)进行交互,以期获得最大的预期利益。上述方法均已被证明适用于FPGA EDA问题的求解过程。

机器学习模型是机器学习方法产出的结果,可以将其视为在给定输入情形下、输出一定结果的函数。机器学习模型并不是一个事先定义好的函数,而是利用历史数据归纳、推导出来的,即当输入不同的数据时,机器学习模型的输出会根据输入的不同而产生相应的变化,但机器学习模型本身并不会发生改变。传统的被应用于解决FPGA EDA问题的机器学习模型包括线性回归、随机深林(Random Forest, RF)以及人工神经网络(Artificial Neural Network, ANN)等。近年来,随着一些大型公共benchmark的公开、算法的突破以及硬件平台计算能力的提升,研究人员开始不断尝试将深度学习模型应用于FPGA EDA问题的求解当中,例如,卷积神经网络(Convolutional Neural Network, CNN)、递归神经网络(Recursive Neural Network, RNN)、生成对抗网络(Generative Adversarial Network, GAN)、深度强化学习(Deep Reinforcement Learning, DRL)以及图神经网络(Graph Neural Network, GNN)等,并取得了令人惊喜的研究成果[26,27]。