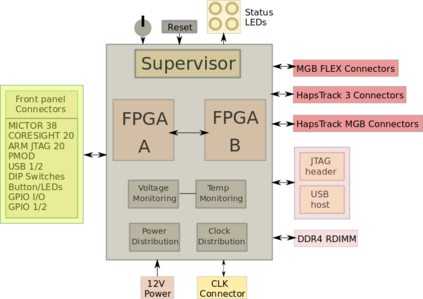

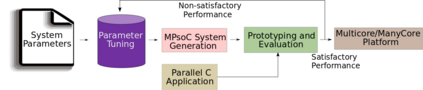

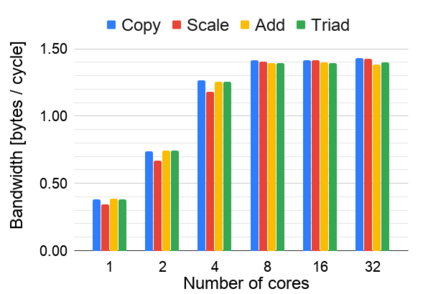

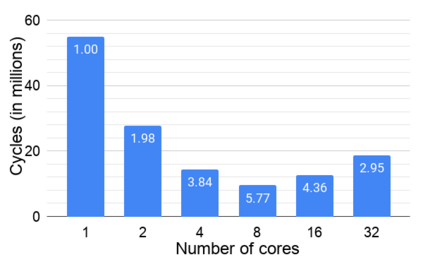

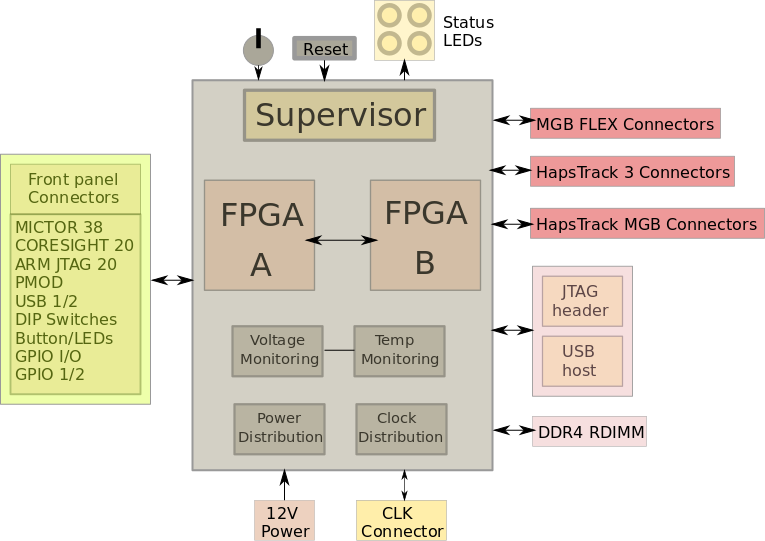

With the growing demands of consumer electronic products, the computational requirements are increasing exponentially. Due to the applications' computational needs, the computer architects are trying to pack as many cores as possible on a single die for accelerated execution of the application program codes. In a multiprocessor system-on-chip (MPSoC), striking a balance among the number of cores, memory subsystems, and network-on-chip parameters is essential to attain the desired performance. In this paper, we present ANDROMEDA, a RISC-V based framework that allows us to explore the different configurations of an MPSoC and observe the performance penalties and gains. We emulate the various configurations of MPSoC on the Synopsys HAPS-80D Dual FPGA platform. Using STREAM, matrix multiply, and N-body simulations as benchmarks, we demonstrate our framework's efficacy in quickly identifying the right parameters for efficient execution of these benchmarks.

翻译:随着消费电子产品需求的增长,计算要求正在成倍增长。由于应用的计算需求,计算机设计师正在试图为加速执行应用程序代码而将尽可能多的岩芯包在单死堆中。在多处理器系统芯片(MPSoC)中,在核心数、记忆子系统和网络芯片参数数量之间取得平衡对于达到预期性能至关重要。在本文件中,我们介绍了基于RISC-V的框架ANDROMEDA,这是一个基于RISC的框架,使我们能够探索MPSoC的不同配置并观察性能罚分和收益。我们在同步心理HAPS-80D双倍FPGA平台上模仿MPSOC的各种配置。我们用STREAM、矩阵增殖和N体模拟作为基准,展示了我们的框架在迅速确定高效执行这些基准的正确参数方面的有效性。