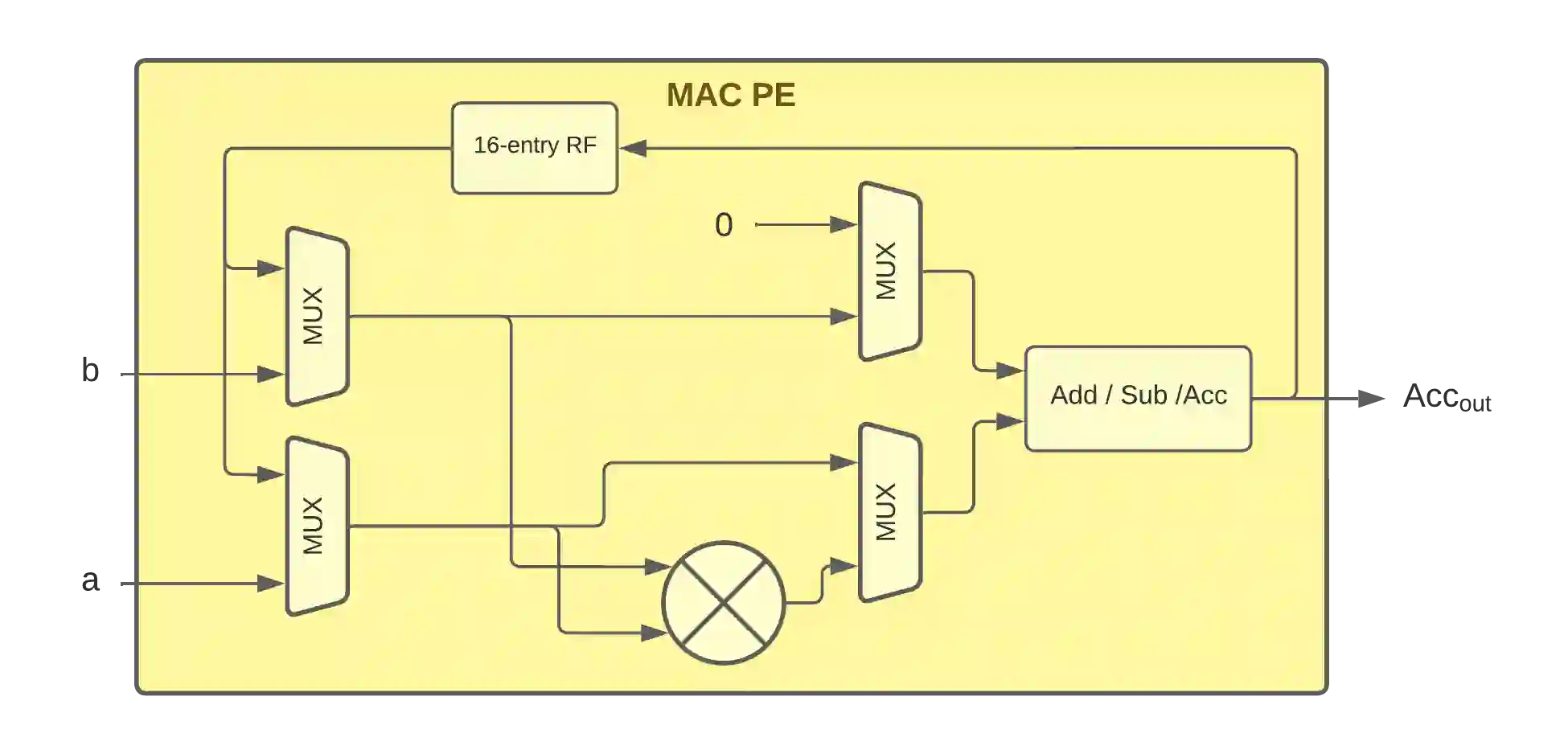

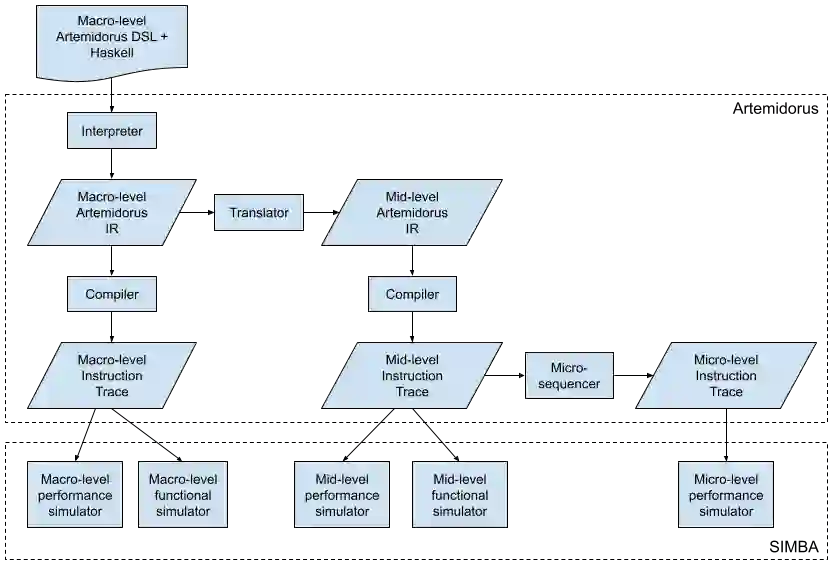

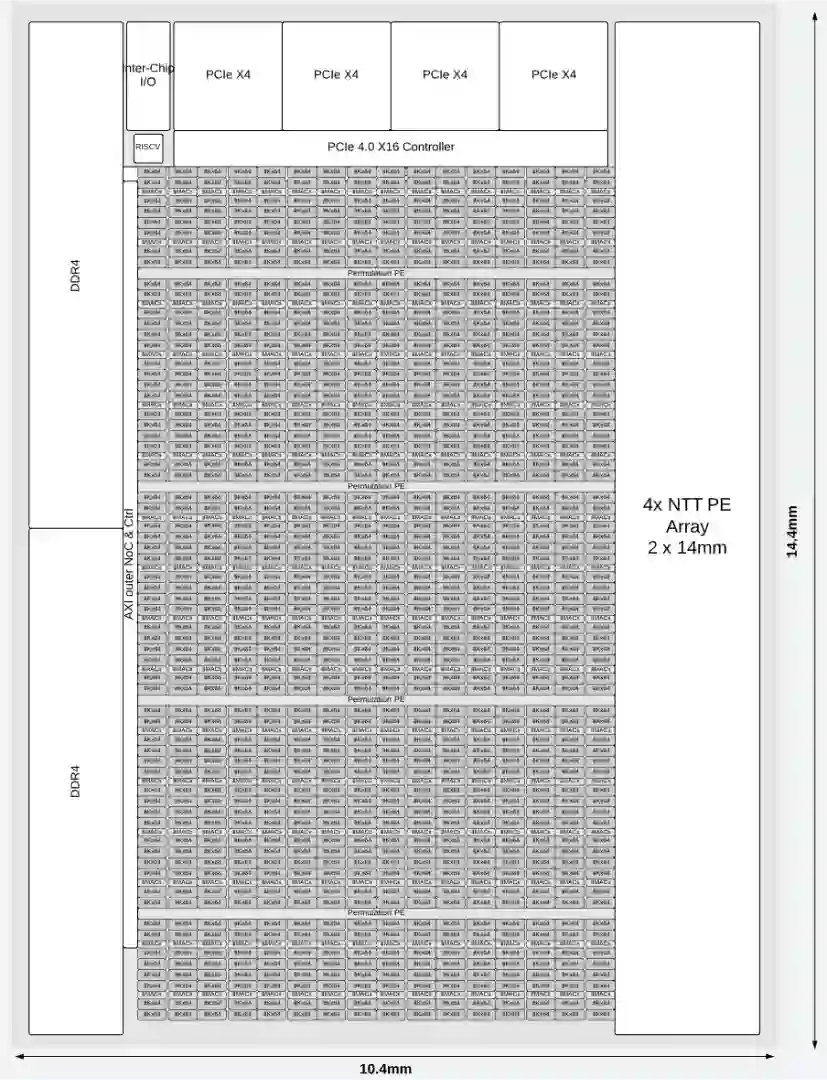

Fully Homomorphic Encryption (FHE) allows for secure computation on encrypted data. We present BASALISC, an architecture family of FHE hardware accelerators that aims to substantially accelerate FHE computations in the cloud. BASALISC implements the BGV scheme, targets a range of parameter sets, and directly supports and implements BGV bootstrapping. We propose a new generalized version of bootstrapping that can be implemented with optimized Montgomery multipliers that cost 46% less in silicon area and 40% less in power consumption. BASALISC is a RISC architecture with a four-layer memory hierarchy, including a two-dimensional conflict-free inner memory layer that enables 32 Tb/s radix-256 NTT computations without pipeline stalls. Our conflict-resolution data permutation hardware is re-used to compute BGV automorphisms without additional hardware and without throughput penalty. BASALISC additionally includes a custom multiply-accumulate unit familiar in DSP architectures, with which we accelerate tight BGV key switching loops. The BASALISC computation units and inner memory layers are designed in asynchronous logic, allowing them to run at different speeds to optimize each function. BASALISC is designed for ASIC implementation with a 1 GHz operational frequency, and is already underway toward tape-out with a 150mm2 die size in a 12nm Global Foundries process.The BASALISC toolchain comprises both a custom compiler and a joint performance and correctness simulator. We evaluate BASALISC in multiple ways: we study its physical realizability; we emulate and formally verify its core functional units; and we study its performance on a single iteration of logistic regression training over encrypted data. For this application, comprising from up to 900K high-level BASALISC instructions down to 27B low-level instructions, we show a speedup of at least 2,025x over HElib.

翻译:完全基因加密( FHE) 允许对加密数据进行安全计算。 我们展示了 BASALISSC, 是一个由 FHE 硬件加速器组成的建筑组, 旨在大大加速云层中 FHE 计算。 BASALISSC 执行 BGV 计划, 目标是一系列参数组, 并直接支持和实施 BGV 靴式。 我们提出一个新的通用的靴式版本, 可以使用最优化的 Montgome 乘数实施, 硅区域成本降低46%, 电力消耗减少40% 。 BASALISSC 是一个有四层内存等级的RISC 结构, 包括一个二维无二维自定义的自动内部内存层, 使32 TBBBx-256 NTT 的内存计算系统。 我们的冲突解析数据配置的自定义的BGFALV 自动自定义的自动自定义自定义自定义的自定义自动智能智能数据, 包括一个自定义的自定义的自定义的自定义的自定义的自定义的自定义的自定义自动自动和自定义的自定义的自定义的自定义的自定义的自定义的自定义的自定义的自定义的自定义的自定义的自定义的自定义的自定义的自定义的自定义的自导和自定义的自定义的自定义的自定义的自定义的自导和自定义的自定义的自定义的自定义的自定义的自定义的自定义的自定义的自定义的自定义的自定义的自定义的自定义的自定义的自定义的自定义的自定义的自定义的自定义的自定义的自定义的自定义的自定义的自导的自导的自导的自导的自导的自导的自导的自导的自导的自导的自导的自导的自导的自导的自导的自导的自导的自导的自导的自导的自导式的自导的自导式的自导式的自导式的自导的自导式的自导的自导式的自导式的自导式的自导式的自导式的自导式的自导式的自导式的自导式的自导