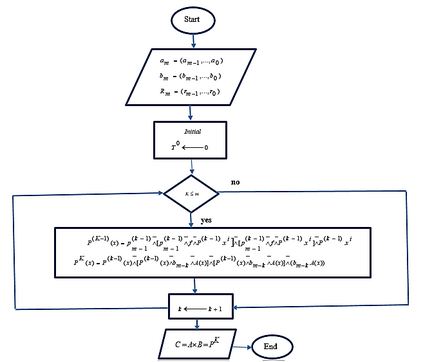

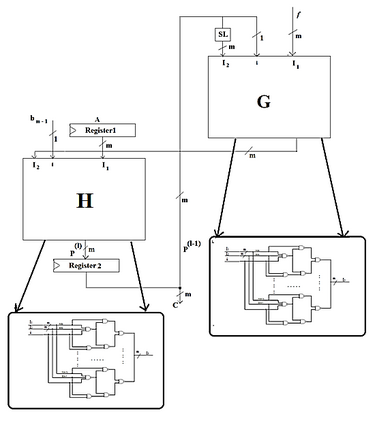

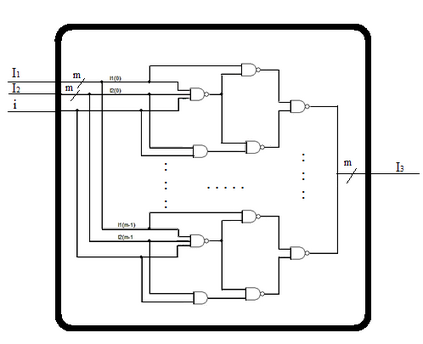

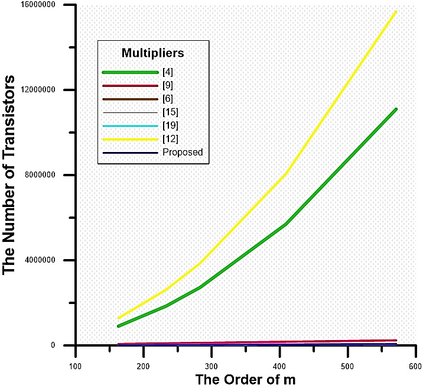

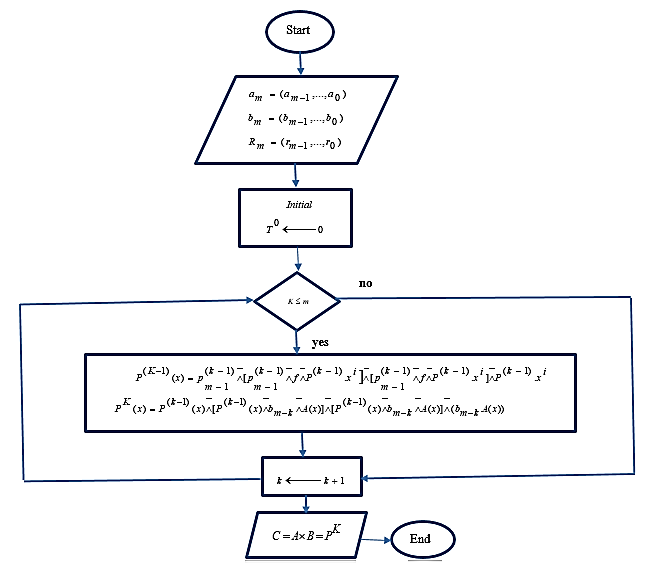

Finite field multiplier is mainly used in error-correcting codes and signal processing. Finite field multiplier is regarded as the bottleneck arithmetic unit for such applications and it is the most complicated operation over finite field GF(2m) which requires a huge amount of logic resources. In this paper, a new modified serial-in parallel-out multiplication algorithm with interleaved modular reduction is suggested. The proposed method offers efficient area architecture as compared to proposed algorithms in the literature. The reduced finite field multiplier complexity is achieved by means of utilizing logic NAND gate in a particular architecture. The efficiency of the proposed architecture is evaluated based on criteria such as time (latency, critical path) and space (gate-latch number) complexity. A detailed comparative analysis indicates that, the proposed finite field multiplier based on logic NAND gate outperforms previously known results

翻译:有限字段乘数主要用于错误更正代码和信号处理; 有限字段乘数被视为这类应用的瓶颈算算单位,是有限的外地GF(2m)的最复杂操作,需要大量逻辑资源; 本文建议采用新的修改的连线并行乘法,并减少分流模块的减少; 与文献中的拟议算法相比,拟议方法提供了高效的面积结构; 使用逻辑NAND门在特定结构中使用逻辑的NAND门,实现了有限的外地倍数复杂性; 依据时间(延时、关键路径)和空间(开关-开关号)等复杂程度等标准对拟议架构的效率进行评估。 详细的比较分析表明,基于逻辑的NAND门的拟议有限外地乘数超越了先前已知的结果。