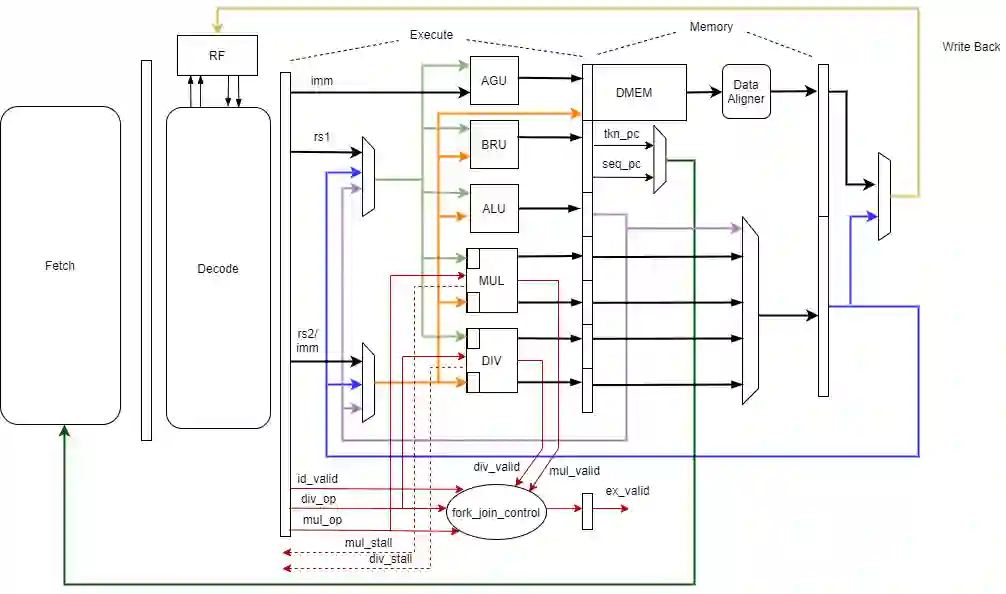

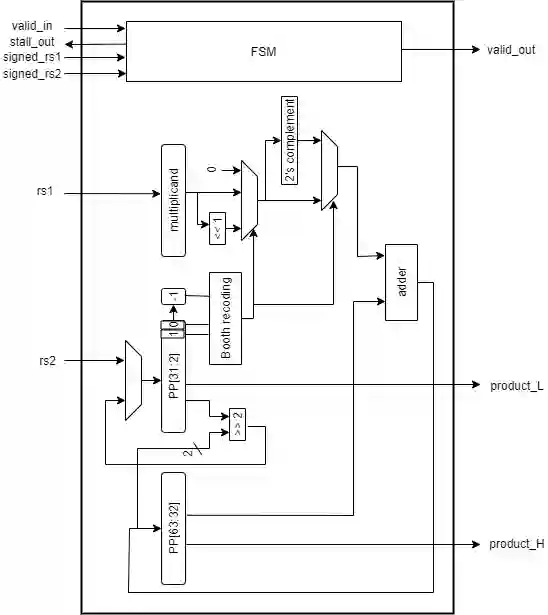

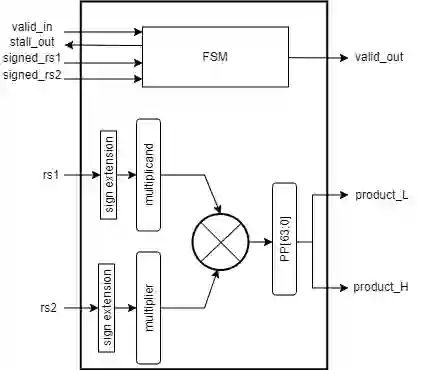

RISC-V, an open instruction set architecture, is getting the attention of soft processor developers. Implementing only a basic 32-bit integer instruction set of RISC-V, which is defined as RV32I, might be satisfactory for embedded systems. However, multiplication and division instructions are not present in RV32I, rather than defined as M-extension. Several research projects have proposed both RV32I and RV32IM processor. However, there is no indication of how much performance can be improved by adding M-extension to RV32I. In other words, when we should consider adding M-extension into the soft processor and how much hardware resource requirements will increase. In this paper, we propose an extension of the RVCoreP soft processor (which implements RV32I instruction set only) to support RISC-V M-extension instructions. A simple fork-join method is used to expand the execution capability to support M-extension instructions as well as a possible future enhancement. We then perform the benchmark using Dhrystone, Coremark, and Embench programs. We found that RV32IM is 1.87 and 3.13 times better in performance for radix-4 and DSP multiplier, respectively. In addition to that, our RV32IM implementation is 13\% better than the equivalent RISC-V processor.

翻译:RISC-V是一个开放的指令设置架构,它正在得到软处理器开发者的注意。 仅仅执行一套基本32位位整数的RISC-V(被定义为RV32I),对嵌入系统来说可能令人满意。 然而,RV32I(RV32I)中没有乘数和分数指令,而没有被界定为M扩展。 一些研究项目提出了RV32I(RV32I)和RV32IM(RV32IM)两个处理器。然而,没有迹象表明通过在RV32I中添加M扩展功能可以改进多少。 换句话说,当我们考虑在软处理器中添加M(被定义为RV32I),以及硬件资源需求会增加多少时,只有32RVC-VC(RVC)软处理器(只执行RV32I)的倍数和分解码,而不是M-M(RV)处理器。 但是,一个简单的叉-join方法被用来扩大执行能力,以支持M- 扩展指令,以及未来可能的改进。 我们然后用Dryst、C(C)和RIM(RM) 3- 和EM) 分别是更好的执行程序。