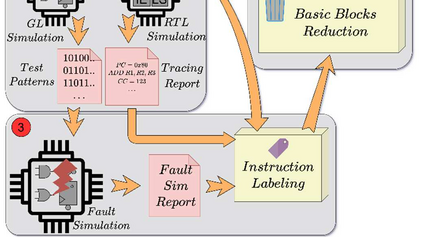

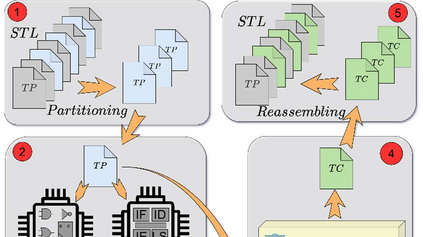

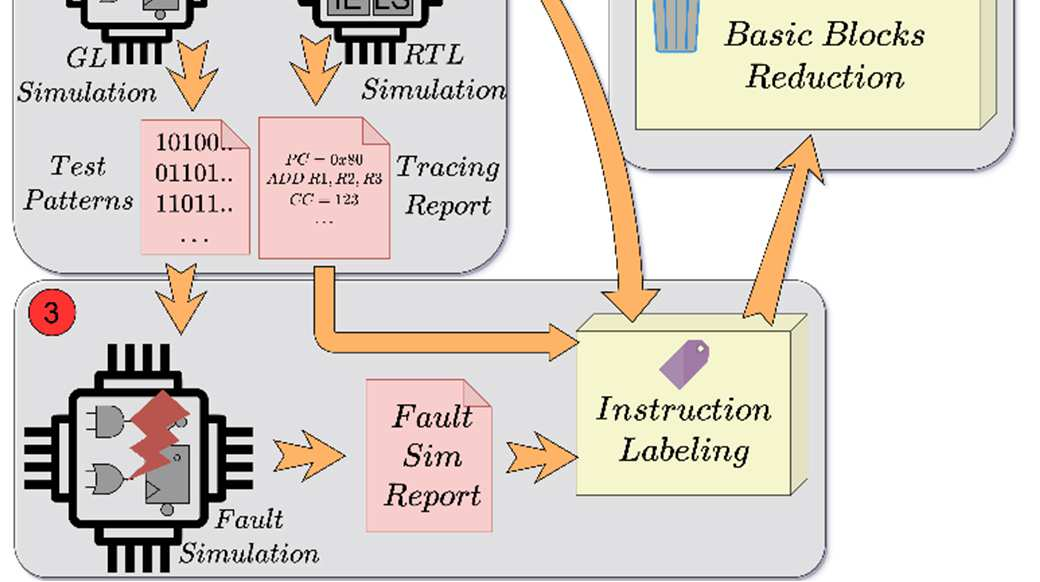

In-field test of processor-based devices is a must when considering safety-critical systems (e.g., in robotics, aerospace, and automotive applications). During in-field testing, different solutions can be adopted, depending on the specific constraints of each scenario. In the last years, Self-Test Libraries (STLs) developed by IP or semiconductor companies became widely adopted. Given the strict constraints of in-field test, the size and time duration of a STL is a crucial parameter. This work introduces a novel approach to compress functional test programs belonging to an STL. The proposed approach is based on analyzing (via logic simulation) the interaction between the micro-architectural operation performed by each instruction and its capacity to propagate fault effects on any observable output, reducing the required fault simulations to only one. The proposed compaction strategy was validated by resorting to a RISC-V processor and several test programs stemming from diverse generation strategies. Results showed that the proposed compaction approach can reduce the length of test programs by up to 93.9% and their duration by up to 95%, with minimal effect on fault coverage.

翻译:在考虑安全临界系统时(例如在机器人、航空航天和汽车应用中),必须对基于处理器的装置进行实地测试。在现场测试期间,根据每种情况的具体限制,可以采取不同的解决办法。在过去几年里,由IP或半导体公司开发的自测试图书馆(STL)被广泛采用。鉴于现场测试的严格限制,STL的规模和时间是一个关键参数。这项工作引入了一种新颖的方法来压缩属于STL的功能测试程序。提议的方法基于分析(逻辑模拟)每项指令所执行的微结构构造操作与其传播对任何可观测产出的缺陷影响的能力之间的相互作用,将所需的缺陷模拟减少到仅一个。拟议的压缩战略通过采用RISC-V处理器和来自不同代代战略的若干测试程序得到验证。结果显示,拟议的压缩方法可以将测试程序的时间缩短到93.9%,其持续时间可以减少到95%,对过失范围影响最小。