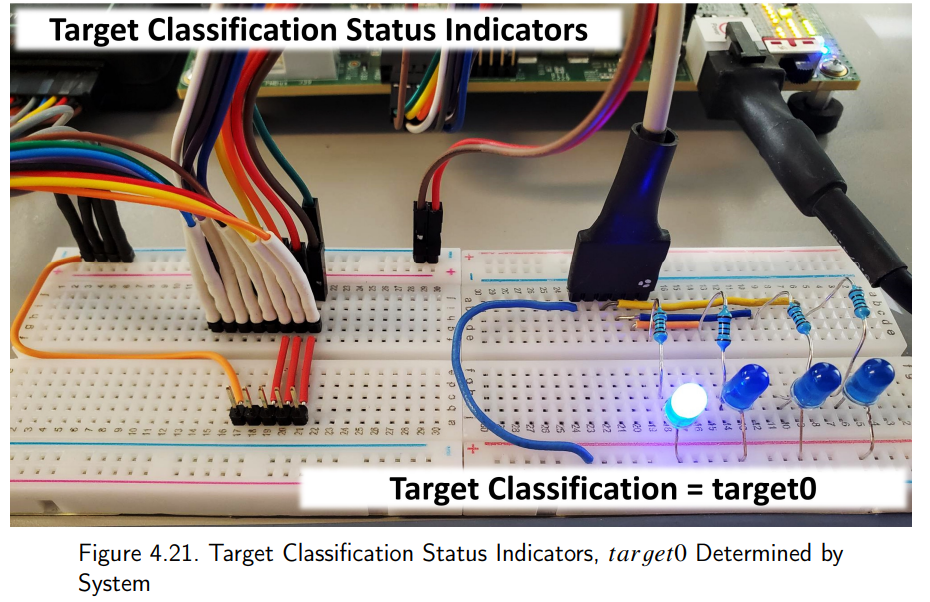

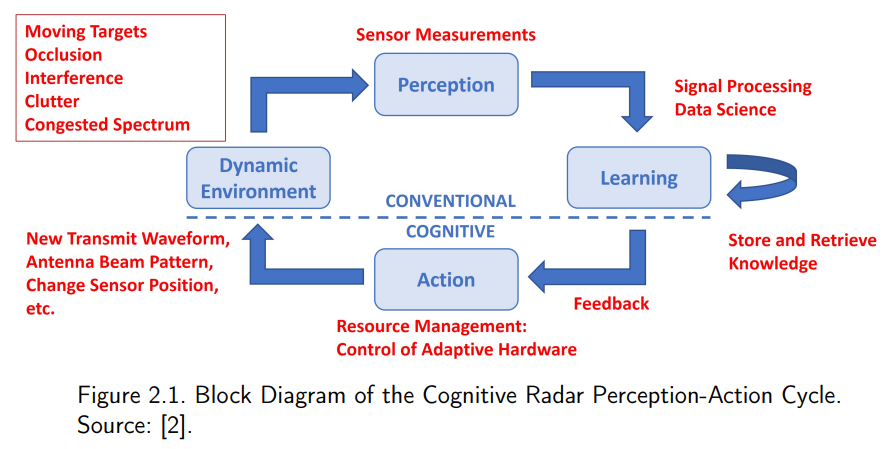

本研究的目的是设计一个用于电子战应用的认知雷达(CRr)目标识别系统的现场可编程门阵列(FPGA)实现。这篇论文对称为加权能量概率(PWE)的闭环自适应匹配波形传输技术进行了扩展。这项工作还研究了在功能性数字硬件实现中应用PWE技术的可行性。最初,在Verilog硬件描述语言中开发了一个PWE蒙特卡洛仿真模型,在Xilinx Vivado环境中进行仿真。然后,在蒙特卡罗模型中开发的Verilog模块组件被整合到利用赛灵思VCU118评估板的CRr目标识别系统实验中。VCU118具有Virtex UltraScale+高性能FPGA,可完成CRr自适应波形生成和传输、数字信号处理要求和目标分类。罗德与施瓦茨公司的SMW200A矢量信号发生器和FSW信号与频谱分析仪分别作为雷达系统的发射器和接收器,而FPGA实现了CRr使用的封闭反馈回路。

目录

- 1 引言 1

- 1.1 论文目的 2

- 1.2 论文组织

- 2 认知雷达的目标识别 3

- 2.1 认知雷达概述 3

- 2.2 加权能量概率理论 4

- 3 Verilog建模和设计仿真 9

- 3.1 Verilog模型概述 9

- 3.2 Verilog模型设计说明 9

- 3.3 Verilog模型结果 36

- 3.4 本章总结 42

- 4 硬件设计和射频实现 43

- 4.1 硬件实现概述 43

- 4.2 闭环雷达配置 43

- 4.3 功能设计说明和演示 57

- 4.4 硬件实现观察 68

- 4.5 本章总结 69

- 5 总结和结论 71

- 5.1 对未来工作的建议 73

成为VIP会员查看完整内容

相关内容

Arxiv

0+阅读 · 2022年7月15日

Arxiv

0+阅读 · 2022年7月13日