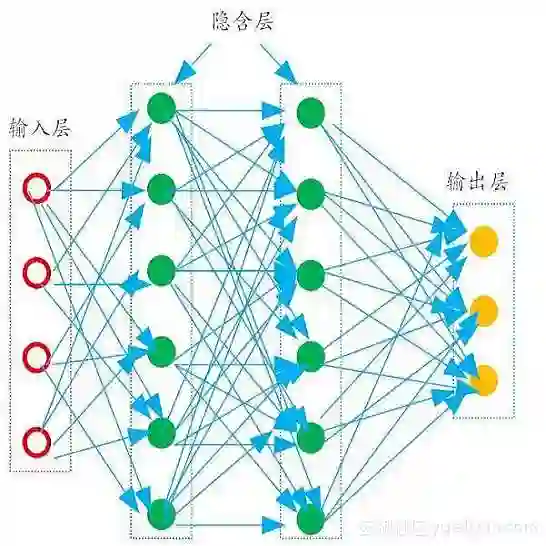

In this paper, we develop an in-memory analog computing (IMAC) architecture realizing both synaptic behavior and activation functions within non-volatile memory arrays. Spin-orbit torque magnetoresistive random-access memory (SOT-MRAM) devices are leveraged to realize sigmoidal neurons as well as binarized synapses. First, it is shown the proposed IMAC architecture can be utilized to realize a multilayer perceptron (MLP) classifier achieving orders of magnitude performance improvement compared to previous mixed-signal and digital implementations. Next, a heterogeneous mixed-signal and mixed-precision CPU-IMAC architecture is proposed for convolutional neural networks (CNNs) inference on mobile processors, in which IMAC is designed as a co-processor to realize fully-connected (FC) layers whereas convolution layers are executed in CPU. Architecture-level analytical models are developed to evaluate the performance and energy consumption of the CPU-IMAC architecture. Simulation results exhibit 6.5% and 10% energy savings for CPU-IMAC based realizations of LeNet and VGG CNN models, for MNIST and CIFAR-10 pattern recognition tasks, respectively.

翻译:在本文中,我们开发了一个在非挥发性内存阵列内实现合成行为和激活功能的模拟模拟计算(IMAC)结构。 利用了旋转轨道磁性磁性随机存取(SOT- MORAM)装置,以实现模拟神经元以及二进制突触。 首先,我们可以看到,拟议的IMAC结构可以用来实现多层感应器(MLP),与以前的混合信号和数字执行相比,达到数量性效绩改进的级级分级。 其次,提议为脉动神经网络(CNNs)推断设计一个混合信号和混合精密CPU-IMAC结构结构。 模拟结果显示,为CPUIMAC系统神经网络(CNNs)的动态神经网络(CNNs)推断,在移动处理器中,IMAC系统设计成一个共同处理器,以实现完全连接(FC)层,而在CPU中执行递增层。 开发了建筑级分析模型,以评价CPU-IMAC结构的性能和能源消耗量。 模拟结果显示,为CUPIIMAM-MAR实现LNet和VGFAR10模式的模型,分别为CIGFAR任务。