基于生成器的集成电路设计流程对于满足快速变化的现代工作负载所要求的积极的系统芯片开发时间表至关重要。生成器允许芯片设计者针对不同的问题开发复杂的解决方案,而不是单独的实例,允许在开发周期的后期进行重大的设计更改,并支持对现有解决方案的增量改进。欢迎不断变化的需求和稳定的增量开发的理念已经被软件开发社区接受了一段时间,但是直到最近才被纳入到硬件开发中。虽然这种经过验证的软件开发理念的采用缩短了片上系统的周转时间,但生产力却受到难以自动化的任务(如物理设计)的限制。每个生成的设计实例都需要一个新的人工生成的平面图或对物理设计流程的其他更改,这限制了可用工程资源对设计空间探索的吞吐量。因此,物理设计的自动化对于最先进的基于生成器的片上系统设计至关重要。

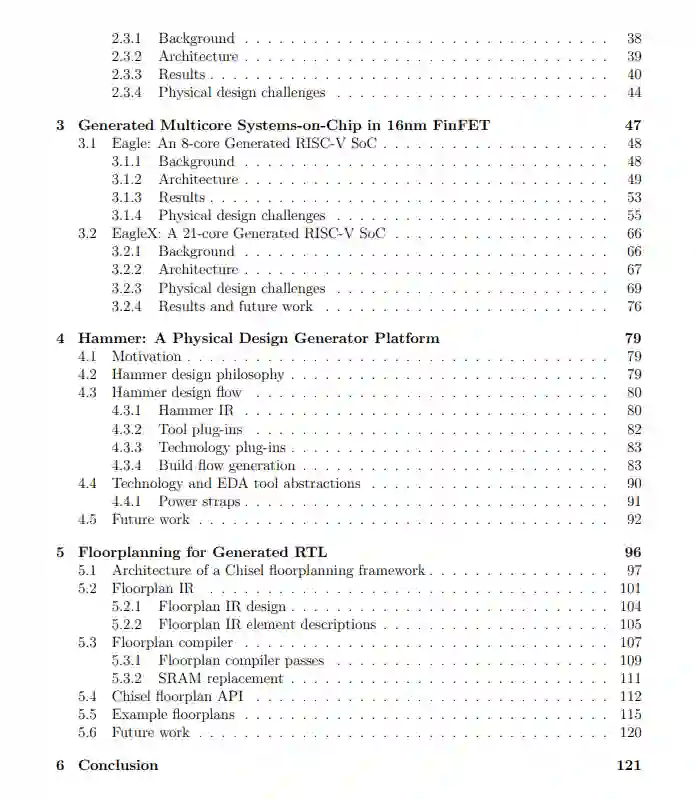

这项工作描述了一系列基于生成器的集成电路,采用28nm FD-SOI和16nm FinFET制造,概述了在其开发中遇到的物理设计挑战,并提出了旨在解决这些挑战的物理设计方法。所介绍的集成电路包括28nm FD-SOI中的8192点数字谱仪、28nm FD-SOI中带有片上细粒功率管理的双核RISC-V矢量处理器、28nm FD-SOI中带有专用片上功率管理核心的双通道RISC-V矢量处理器、16nm FinFET中的8核RISC-V矢量机和16nm FinFET中带有收缩阵列加速器的21核RISC-V矢量机。该八核芯片在半精度矩阵乘法(GEMM)内核上实现了最先进的209.5 GFLOPS/W的能源效率。

本文提出的物理设计方法使用框架Hammer,通过解耦特定于设计、特定于工具和特定于技术的后端设计方面,以及用于两个Chisel设计的新平面图生成框架,提供可重用的物理设计交付物。这种物理设计方法已被纳入Chipyard框架,这是一个利用Chisel硬件构建语言的开源RISC-V片上系统开发平台。平面图生成框架允许生成RTL的Chisel程序指定可组合的平面图,而无需修改原始源代码。该流程解决了与平面规划生成RTL相关的常见挑战,如SRAM映射和放置,展示了平面规划生成在减少基于生成器的设计开销和周期时间方面的有效性。