专用硬件加速器已被开发用于提高深度神经网络(DNN)应用的能效比。

在DNN加速器开发中,一个主要挑战是对设计原型在真实世界应用中的早期阶段评估。这种评估至关重要:现代DNN加速器配备了多种技术以提升能效,但这些技术可能引入数值误差,例如通过定制化数值表示进行的数据量化或重新设计的运算符。鉴于DNN应用具有深度连接的分层特性,这些数值误差可能积累并导致结果与参考结果产生显著偏差。此外,主机机器与加速器片上存储器之间的数据传输在能耗和性能方面的成本相当高,这使得减少数据传输成为将DNN应用映射到加速器时的关键优化重点。 为了解决这些挑战,本论文提出了若干创新性解决方案。

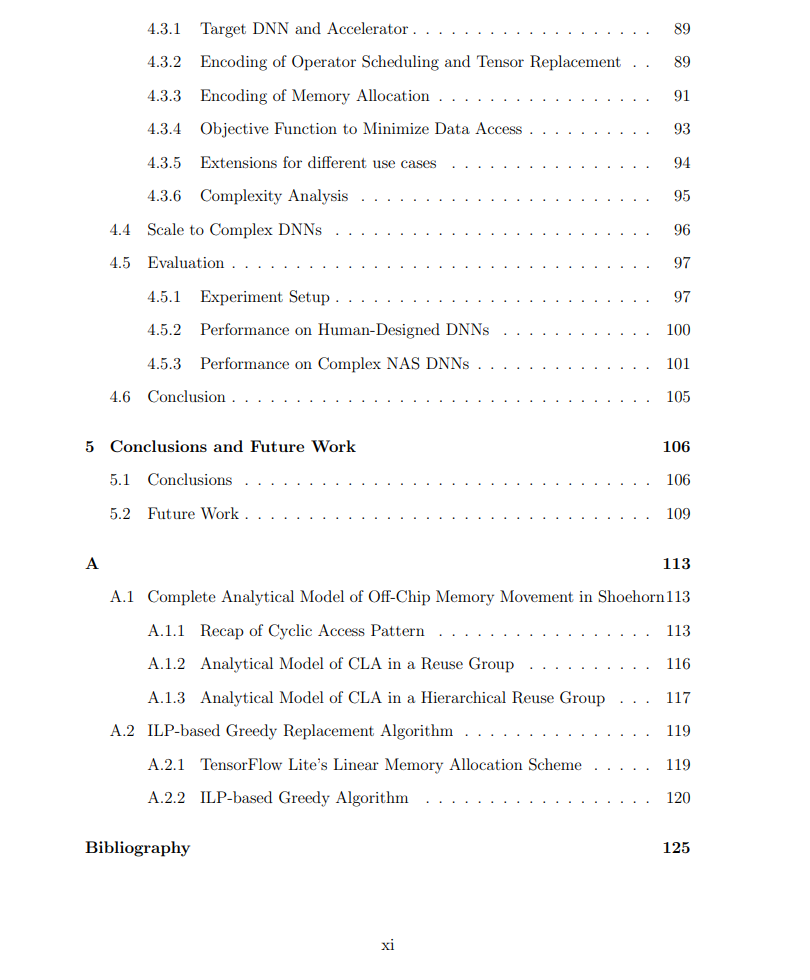

首先,我们引入了“3LA”——一个端到端的编译器流水线,用于在未经修改的DNN应用上进行硬件加速器原型的应用级测试。基于最近提出的名为指令级抽象(Instruction-Level Abstraction,ILA)的形式化硬件规范,3LA实现了自动化的应用级模拟,从而显著减少了手动工程工作量,并提供了关键的开发反馈。 其次,我们提出了 Shoehorn,一种针对将DNN算子映射到硬件加速器的优化调度器,它协同优化循环分块、循环排序以及片上存储分区决策。此调度器为单个应用级算子生成针对特定加速器的最优映射计划,最大限度地减少片外存储访问。 最后,本论文介绍了 COSMA,一个优化框架,旨在部署整个或部分DNN应用至目标加速器时,最小化总片外数据访问量。COSMA通过集成优化算子调度、存储分配和张量替换策略,提供了一种全面的数据移动最小化解决方案。 这些贡献有望显著简化从早期设计到最终应用部署的DNN加速器开发过程,提升该领域的效率和效果。

成为VIP会员查看完整内容

相关内容

Arxiv

36+阅读 · 2023年4月19日

Arxiv

185+阅读 · 2023年4月7日