「垂直晶体管技术突破可以帮助半导体行业继续其前进道路,实现重大改进,包括全新的芯片架构,待机时间长达一周的手机,更低能耗的 IoT 设备等等。」本周二,IBM 和三星提出了一种全新芯片制造工艺 VTFET,相比 FinFET 可以有两倍性能提升,或者减少 85% 能耗。

在试图把更多晶体管装入有限空间的努力过程中,VTFET 工艺解决了许多以往解决不了的性能障碍。它还能让晶体管使用更大的电流,同时减少了能源浪费。

![]()

VTFET 为延续摩尔定律找到了一条途径,不知这种工艺何时能够落地,制成芯片落到我们的手中。

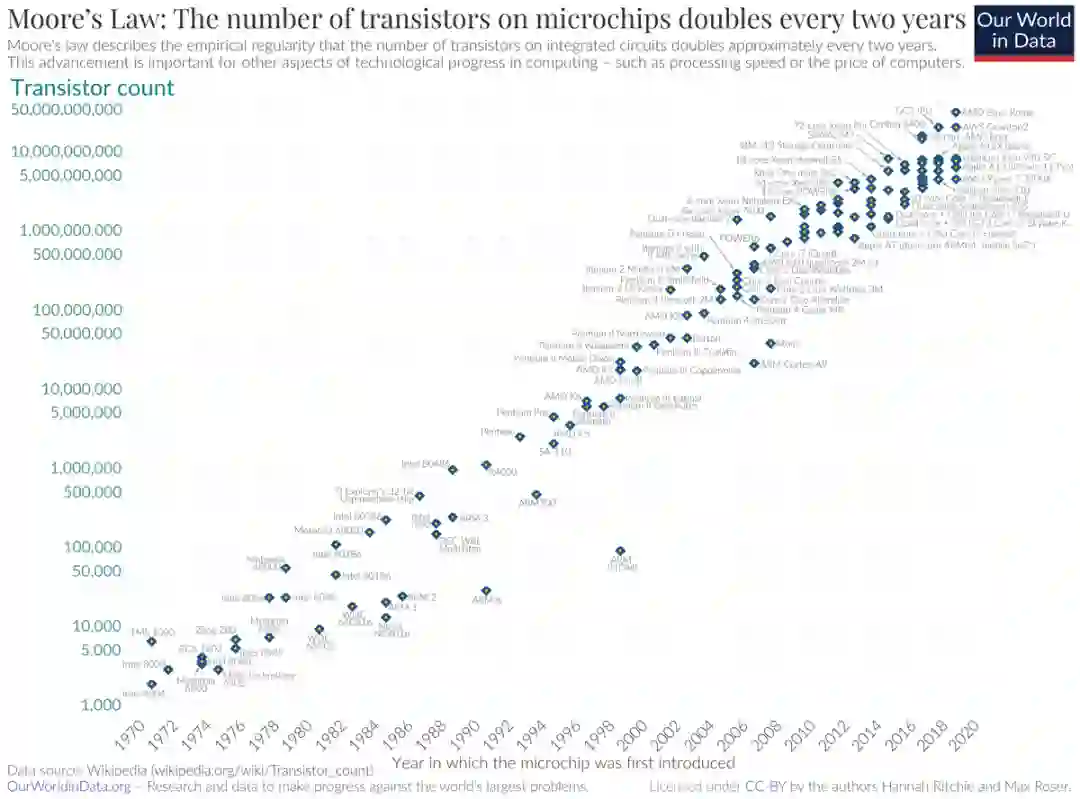

早在 1965 年,计算机科学家戈登 · 摩尔(Gordon Moore)首先提出假设:集成电路上可以容纳的晶体管数目在大约每经过 18 个月便会增加一倍,同时计算机的运行速度和存储容量也翻一番。这就是半导体领域著名的摩尔定律。当前,可以塞进单个芯片的晶体管数量几乎达到了极限。

![]()

但与此同时,计算系统的前进道路并没有放缓。动态 AI 系统已准备好为人们生活的方方面面(从道路安全到药物发现和先进制造)提供动力,这就需要未来出现性能更强大的芯片。因此,为了延续摩尔假设的速度和计算能力的进步,我们需要制造具有多达 1000 亿个晶体管的芯片。

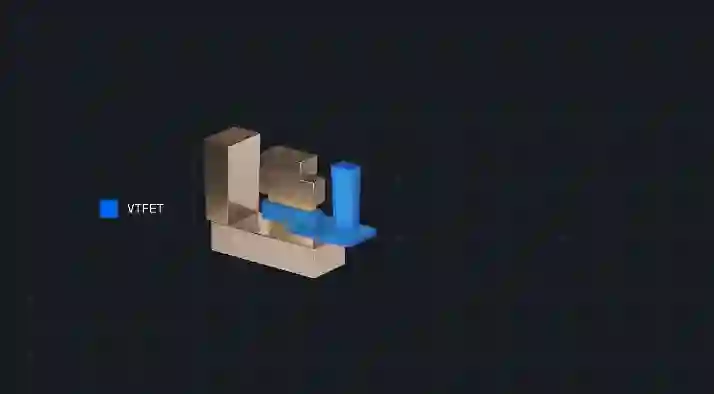

IBM 研究院与三星合作,在半导体设计方面取得了突破性进展,声称有助于摩尔定律在未来几年保持活力,并重塑半导体行业。他们提出了一种在芯片上垂直堆叠晶体管的新方法,称为垂直传输纳米片场效应晶体管(Vertical-Transport Nanosheet Field Effect Transistor, VTFET)。如下为 VTFET 晶圆示意图:

![]()

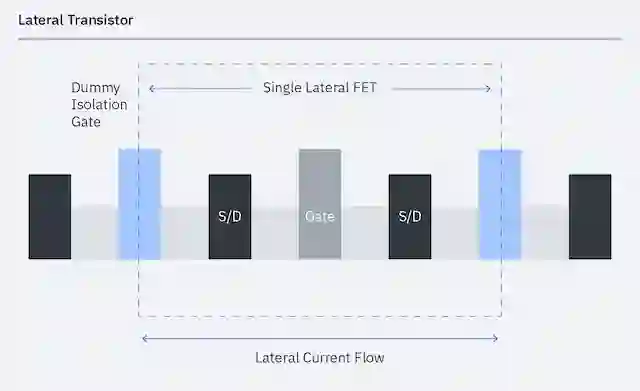

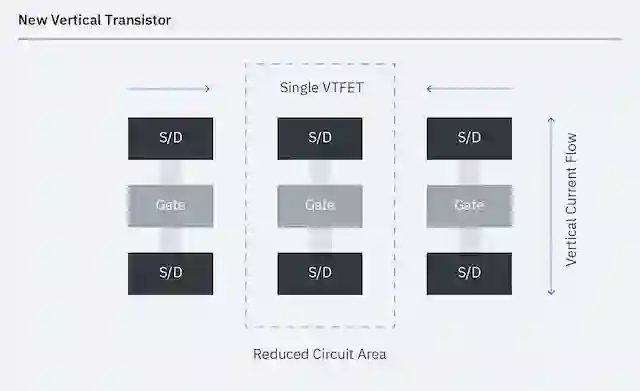

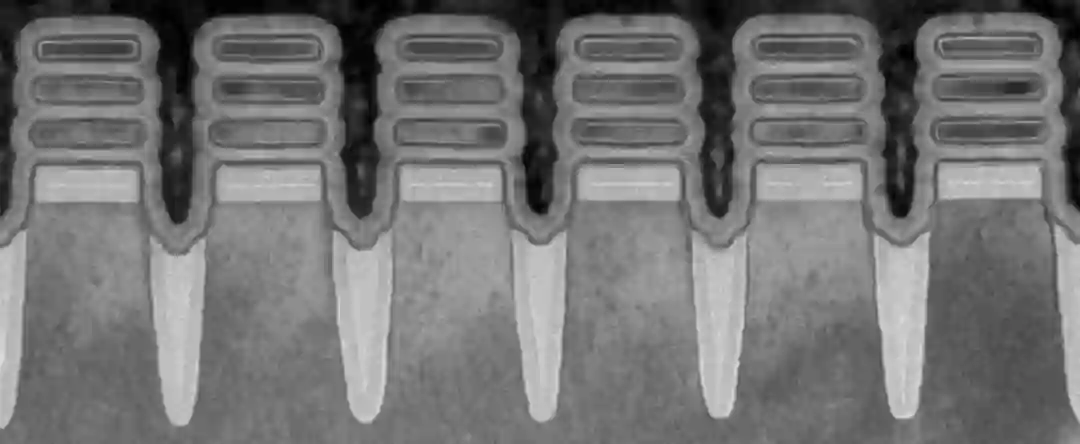

当今,主流的芯片架构采用横向传输场效应晶体管(FET),例如鳍式场效应晶体管(FinFET),因硅体类似鱼背鳍而得名。finFET 在设计上沿着晶圆表面对晶体管分层,电流沿水平方向流动。与这类设计不同的是,VTFET 是在

垂直于硅晶圆的方向上将晶体管分层,并允许电流在堆叠晶体管中上下流动。

下图为接通电流时,VTFET(左)和横向 FinFET(右)晶体管组合结构的并排比较。

![]()

这种新的设计方法通过放宽晶体管门长度、间隔厚度和触点尺寸的物理限制来解决缩放(scaling )障碍,并在性能和能耗方面对这些功能进行优化。

下图(左)为 VTFET 设计师和项目经理 Brent Anderson,(右)为硬件技术专家和主要研发成员 Hemanth Jagannathan,他们在展示 VTFET 晶圆。

![]()

通过 VTFET,IBM 和三星成功地证明了在 CMOS 半导体设计中,探索纳米片技术以外的缩放性能是可能的。在这些先进的节点上,与按比例缩放的 FinFET 替代方案相比,VTFET 能够提供两倍的性能提升或者减少高达 85% 的能耗。

![]()

今年 5 月,IBM 就发布了全球首款采用 2nm 制程工艺的芯片,每平方毫米容纳 3.33 亿个晶体管,号称可以将 500 亿个晶体管集成到一个指甲大小的芯片上。据当时的介绍,IBM 这款 2nm 芯片的晶体管采用的 three-stack GAA 设计。

![]()

此次,VTFET 延续技术创新,用垂直堆叠晶体管的方法打开了新的可能。

过去,设计师通过缩小栅极间距和布线间距将更多晶体管封装到芯片上。这种适合所有组件的物理空间被称为接触式栅极间距(Contacted Gate Pitch, CGP)。缩小栅极和布线间距的能力使得集成电路设计师将设备中能够容纳的晶体管从数千个增加至数百万乃至数十亿。

然而,即使是采用最先进的 FinFET 技术,间隔、栅极和触点的空间依然是有限的。一旦达到 CGP 的极限,也就没有扩展的空间了。

在晶圆上水平排列层的 FET 配置。需要使用图中蓝色虚拟隔离门来隔离浪费空间分离相邻电路。

VFET 配置在晶圆上的垂直排列层,通过缩小栅距和消除虚拟隔离栅显著提高了密度。

由于垂直定向电流、栅极、空间和触点不再受传统方式的限制,我们有了更多空间扩展 CGP,同时保证了健康晶体管、触点和隔离(隔离和浅沟槽隔离,STI)的位置。由于摆脱了横向布局和电流方向限制,我们能够使用更大的源 / 漏触点来增加器件上的电流。

我们还可以选择栅极长度来优化器件引导电流和泄漏,而隔离层厚度可以独立优化以降低电容。我们无需被迫在栅极、隔离和触点尺寸之间进行权衡,这可以提高晶体管速度并降低功耗。

VTFET 另一个关键的特性是能够将 STI 用于相邻电路隔离,以实现零扩散中断(ZDB)隔离,而不会损失有源栅极间距。相比之下,横向传输的 FET 电路密度受到电路隔离所需的单双扩散的影响,这会影响进一步缩小晶体管尺寸的能力。

即使是在十年以前,我们也能感受到横向架构会在激进的栅极间距下达到规模限制,实际上在芯片中的所有的组件都已接近极限。IBM 提出的方式旨在寻找打破这些障碍的途径。

由于栅极间距比生产中已知的任何产品都更加激进,且硅晶片栅极间距低于 45 nm 的 CMOS 逻辑晶体管。IBM 相信,VTFET 设计代表着构建下一代晶体管的巨大飞跃,这将使未来几年出现更小、更强大和更节能的设备。

https://www.youtube.com/watch?v=OF3Zwfu6Ngc&t=1s

https://research.ibm.com/blog/vtfet-semiconductor-architecture?lnk=ushpv18nf1

![]()

© THE END

转载请联系本公众号获得授权

投稿或寻求报道:content@jiqizhixin.com