业界 | 深度学习芯片公司Graphcore初探:颠覆GPU、FPGA和CPU的新一代处理器IPU

选自Nextplatform

作者:Nicole Hemsoth

机器之心编译

参与:朱朝阳、侯韵楚、李亚洲、黄小天

作为思维锻炼,让我们将神经网络视为大量的图形,把 CPU 视为一个更高级命令处理器的被动从属设备,这个处理器可在不断扩展的连接网络上跨多点进行训练、推断,并在同一架构上自我分化成多个模型。

当然,在这个概念中可能会有大量的技术性否定,且只有一部分与算法复杂性有关。首先,至少对于神经网络问题来说,即使在诸如 GPU 和 FPGA 的专用设备上,内存带宽也到达了极限。第二,即使保持存储消耗的供给不是瓶颈,软件开发任务也会随问题而扩展。架构定制是大规模提高神经网络速度的唯一办法。这并不排除通用加速器,因为确实需要它们去完成任务。

退一步讲,真正的问题是如果新一代处理器要颠覆 GPU 或 FPGA,又或是可靠的 CPU,它应该具备哪些性能?有些情况下,这种处理器看起来像是一个(经常被堆栈的)内存设备,可以掌控整个模型,并通过最小化(或至少减少)片外存储器访问来减少延迟;其他情况下,它看起来又更像是一个专门被架构的用于快速输入/输出的计算图形处理器 :带有一个自定义互连,大量但简单的内核,并可在鲁棒的编译器之后大规模地解决所有凌乱的图形处理问题。

一些人会认为 Pascal GPU 已能做到这一点,并会继续发挥更大作用,因为它们擅长处理神经网络算法中稀疏性问题。但是调优的架构却牺牲了性能和效率。关键在于,如果存在一种训练与推断同样高效的图形架构,它可能会颠覆整个行业。如果深度学习的早期阶段有令人垂涎的奖励,尤其是当用户池足够浅从而可一眼看穿时,一个两全其美的架构就有可能出现在行业之中。

像许多我们交流过的做机器学习芯片的供应商和研究人员一样,Graphcore 认为其取得了突破性进展,提升了可延展性,恰当地平衡了性能/电源。Graphcore 还认为通过一个图形处理器做可以解决所有问题,并最终可让智能处理单元(或 IPU,如其所名)在同一架构上跨多个形状因子(服务器和设备)地承担训练与推断的双重任务。你猜怎么着?他们确实为上述所有情况做了最好的打算。也就是说他们声称的可以在新一代的高带宽/堆栈内存上获得 100 倍的内存带宽加速,这确实是真的。关于这一点,谈论硬件时会提及更多,2017 年底是 TSMC(如 Pascal GPU)的 16 纳米 FinFET 早期用户预定的交付日期。

Graphcore 的 CEO Nigel Toon 向 *The Next Platform *提供了关于其所做事情的极其详细的信息,他在特定工作负载的专用架构设计上很有经验,作为一名前 IPO 场应用工程师在 FPGA 芯片制造商 Altera 工作超过 10 年,并在多家聚焦于高调试硬件设备的单一性业务初创公司(被 Nvidia 和 Broadcom 收购)工作过。Graphcore 工程团队的大部分人都有类似的背景。而且,他还说,Graphcore 知道如何瞄准一个特定应用程序集并打造其他公司肯定也在做的适配性东西,只是没有做到像 Graphcore 这样强调互连和底层软件堆栈。

「设计出的这一架构可同时适合训练和推断。在某些情况下,你可以设计一个可用于训练的硬件,然后将其分段或虚拟化以支持许多不同的用户进行推断甚至是不同机器学习模型的部署。存在如下情况,例如,当一切被嵌入之后,并且你需要一个稍微不同的实现,但它却是同一个硬件架构。这是我们的主题:唯一架构 IPU,可用于训练、推断,并可完成被用于服务器、云或网络边缘的机器的不同实现。

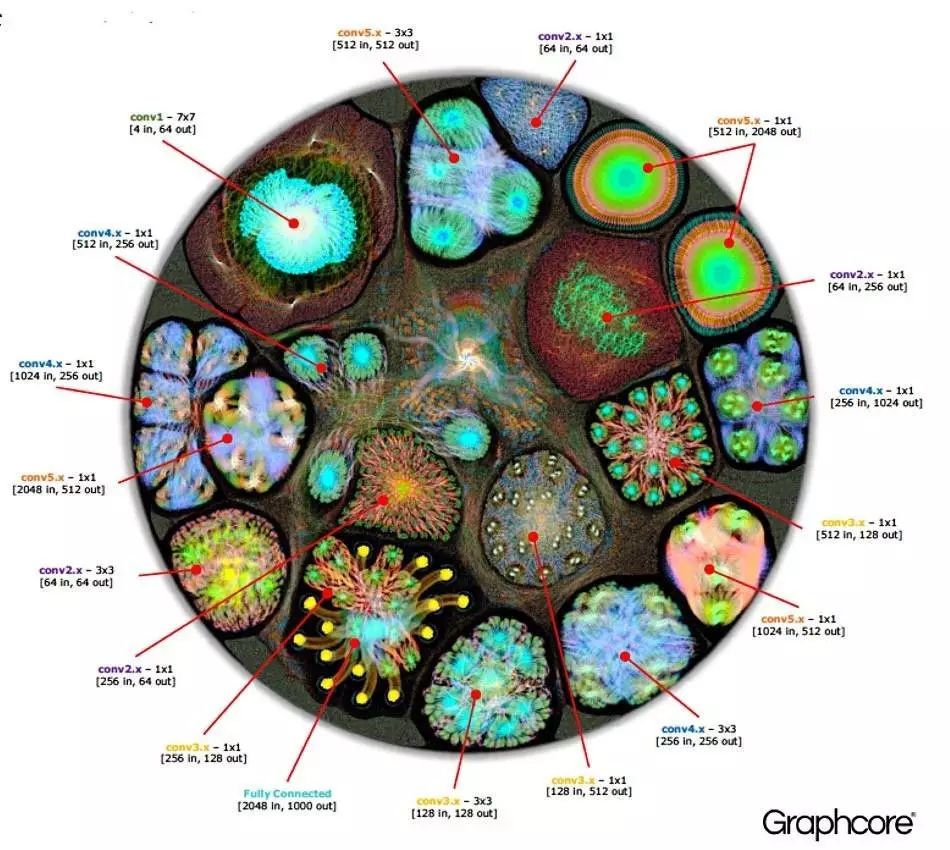

Graphcore IPU 的核心是一个图形处理库。「如果查看底层机器学习工作,需要捕获数据精华,即从数据中学到的一组特征和这些特征之间关系。这可表示为一个神经网络模型,或者更准确更通俗地说,是一个计算图形,它的一组边表示关联权重的数据,边上的顶点表示计算函数,」Toon 解释道。「你正在尝试在图形上理解这些特征和它们之间的关系。该图形的构建很复杂,且是多层的,因为你得到了这些关系的不同的层面。」问题也不会就此结束。神经网络的总体规划是创建越来越大的网络,彼此循环,学习和改进。这些必须是循环的——不只是以 RNN 方式,而且要在许多层和网络中循环。总之,最终结果是深入,宽泛的强化学习,或更简单地,建立在使用不断改善的网络。正如人们可以想象的那样,这种任务的计算负荷是巨大的,并且比简单地投入 CPU 来喂养它更加微妙,即使它最容易线性地(在理论上)扩展。

说到理论,建立一种自我馈送、自我学习的网络将带来重大挑战:抵达最专业设备的当前极限。

Graphcore IPU 的技术直到今年下半年才予以公开,尽管未提及任何与现存架构有关的细节,但我们仍旧发现了一些有趣的新东西。首先,整个神经网络模型适合于处理器(而不是存储器)。这上千块简单内核并不依赖通往外部储存器的狭长而延迟的路径,它们可以进行内部存储而不产生跳跃。Toon 的说法最有意思:「即使尽力添加 HBM 和 3D 堆栈,你指的仍旧是在 700 GB 每秒的数量级水平访问外部储存器,而我们通过将模型置于处理器内,在外部储存器中约有 100X 的带宽到内存」。当然,这里指的是设备的总内存带宽。

Toon 说:「我们正在尝试将图形映射到图形处理器,即 IPU 中。其关键是要让软件允许采取这些复杂结构,并映射到一个将维持模型所需的全部内存包含在内,且高度并行的处理器中。将神经网络扩展成图形后,软件便会将它映射到一个相对简单的处理器中,这个处理器有些属性很有趣,如一个完全由编译器控制的十分丰富的互连系统。互连和内核本身便具有许多创新——我们使用的不是标准内核,在一个芯片上有一千多个。」他指出,这是真正的千块内核,能够与 Nvidia 分割 56 个处理器块而成的大量内核相比。他说:「这是 Nvidia 面临的困难,也是我们在努力解决的问题——在 GPU 情境中,若要在 56 个块间使用 GPU 共享数据,我能做到的唯一方法是写入外部存储器后再次读回。」他说,为数千内核构建架构需要一个不同的结构——它不依赖于推送数据至外部存储器,在内部共享并置于处理器中,且在所有内核之间负载平衡。

因此我们可以假设这种架构和一些非标准内核可能存在自定义互连,所以下一个问题便与精度有关——一个 Nvidia 所擅长的,使用 Pascal 处理工作负载的领域。提取关于这些芯片具体作用的信息很难,但若以提示的方式,Toon 说:「实际情况是,你需要对某一点提供 32、16 及量化整数的支持;但不需要双精度,那是在浪费硅。」

「整个模型都处于处理器内部,所以认为内存作用于处理器并不妥当,但处理器具有前所未见的内存级别,进而能够在内部存储这些复杂模型,这使计算得以更高效地部署,来操纵模型中高度稀疏的数据结构……我们拥有能够简化编译器的复杂指令集——如果你能使一个处理器易于编译,就有可能使编译器更具复杂性。若指令集相同,它们会在同一周期中运行,并且我能运行更多操作,从而使编译器更具复杂性。」

图形方法使机器学习用户的结构能够暴露大量并行性(比如,每个顶点可能有 2500 万个参数),这是可以应用于大型并行机器的大量并行计算。但数据中同样存在麻烦的层和关系级别:一个顶点也许能够与几十甚至几千个其他顶点相连接,而这些顶点自身又与许多其他顶点相连。因此,尽管想要将图中的数据映射到传统的线性寻址存储器中,却只有距离最近的两位「邻居」,而真正需要的却是能够在大量存储器中散布的东西(这同样需要进行操作、编写返回等等)。重点在于,我们需要的是能够在几乎无限的存储器带宽约束中收集数据并编写返回的机器。这便是引起一片哗然的稀疏问题,但 Toon 说他们已经完成了这个挑战。

谈及稀疏问题时,Toon 认为用户正将计算元素浪费在大型向量中。「回到训练与推理的矛盾问题。在训练中,你牺牲了内存大小来诱导一些数据并行性,使之适用于一个向量(如为了图像训练而并行化为小批量),并用这些小批量在宽向量的 GPU 上填充向量。但问题的每个计算阶段都要对内存进行乘法运算,所以不可能进行推断,因为有一个新的数据要理解——没有任何一组数据并行且输入机器,而这就是 GPU 在推理中为什么低效的原因」。

Toon 说,训练和推理只是对图形的操作,它的计算密集度更高,因为图形必须通过许多层和迭代来建立正确的特征和权重;但对推理而言,部署这样的服务可能需要数千用户有很大的计算量。「倘若我能成功构建一台能够进行训练和推理,同时在图形结构方面也很高效的机器,那么这将有助于我打造在时间中不断学习、越来越好的未来网络」。

今年下半年我们会得到一个完整的简报,帮助我们把它正确置于游戏中并完全理解其中的互连与核心故事(core stories),更不用说,还包括设备中蕴含大量内存的魔法球环绕在何处。当 CPU 在占有服务器市场,并且在目的过于通用的 GPU 为了互连或带宽而无休止地削减硬件(面对不断增长的模型复杂性)的同时,Toon 也在进行倒计时。

在后续文章中,我们将通过描述 Graphcore IPU 基于 C ++ 和 Python 的「Poplar」软件框架,来给予更多提示。

原文链接:https://www.nextplatform.com/2017/03/09/early-look-startup-graphcores-deep-learning-chip/

本文为机器之心编译,转载请联系本公众号获得授权。

✄------------------------------------------------

加入机器之心(全职记者/实习生):hr@jiqizhixin.com

投稿或寻求报道:editor@jiqizhixin.com

广告&商务合作:bd@jiqizhixin.com