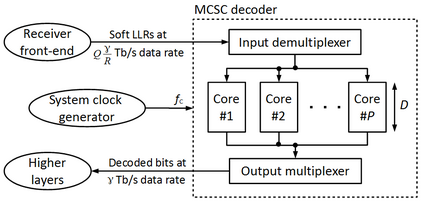

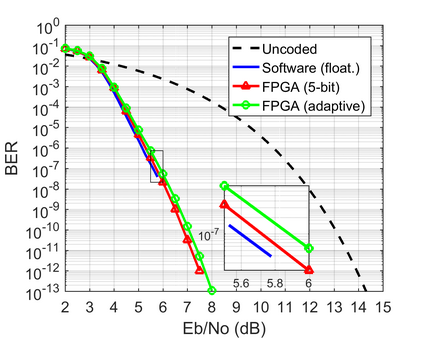

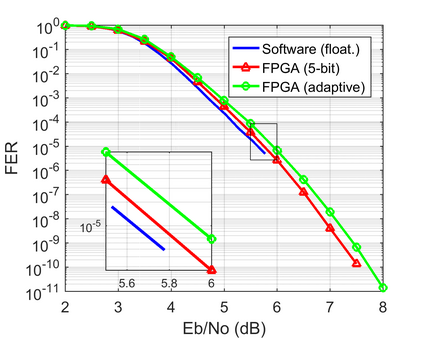

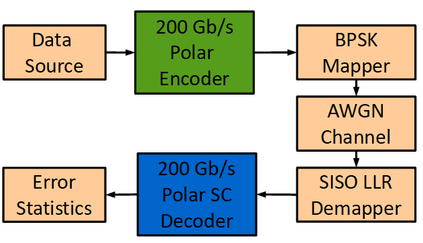

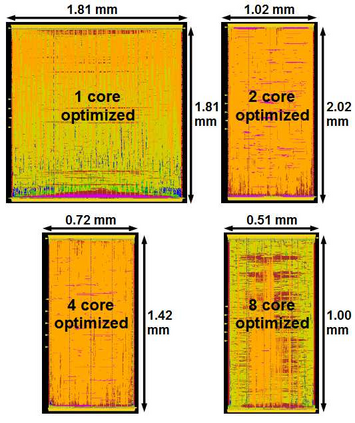

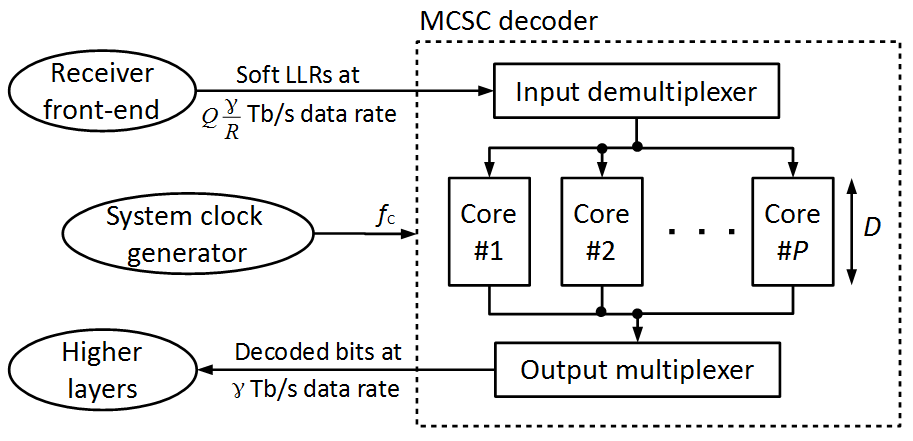

This work presents a high throughput and energy efficient multicore (MC) successive cancellation (SC) decoder architecture for polar codes. SC is a low-complexity decoding algorithm with a set of sequential operations. The sequential processing nature of SC limits parallelism but promotes not only pipelining but also multiple copies of SC decoder with an optimized pipeline depth to achieve Tb/s throughput. The MCSC decoder architecture consists of multiple SC decoders with lower frequency and pipeline depth to process multiple codewords in parallel to achieve lower power consumption. The pipeline depth of MCSC is optimized separately for each multicore configuration using register reduction/balancing (R-RB) method. This enables an efficient implementation for the 1-core, 2-core 4-core and 8-core candidate MCSC decoders. To reduce the complexity of the implementation, an adaptive log-likelihood ratio (LLR) quantization scheme is used for internal LLRs within the range of 1-5 bits. The post-placement-routing results at 28nm High-k Metal Gate (HKMG) ASIC technology show that 4-core MCSC decoder achieves 1 Tb/s throughput on 3.92 mm$^2$ area with 1.55 pJ/bit energy efficiency.

翻译:这项工作为极地代码提供了高吞吐量和高能效的多核心(MC)连续取消(SC)解码器结构。SC是一种低复杂度解码算法,具有一系列相继操作。SC的顺序处理性质限制了平行性,但不仅促进了管道线,而且还促进了多份具有最佳管道深度的SC解码器,以达到Tb/s通过量。MCSC的解码器结构由多个频率和管道深度较低的SC解码器组成,以平行处理多个代码字,以降低电力消耗。MSC的管道深度是使用登记减少/平衡(R-RB)法,对每个多核心配置分别优化的管道解码算法。这有利于高效实施1核心、2核心4和8核心候选的MCSC解码器。为了降低实施的复杂性,在1至5位贝范围内对内部LLLR(LLR)采用适应性log-类似比例的昆化计划。在28nm高金金属门(HKMG)的安装后,使用减少/平衡(R-RB)方法优化了管道深度。这有利于高效执行1至1级的ASISIC技术,显示在1个领域实现4核心效率。