Google大神Jeff Dean最新DAC演讲《机器学习在硬件设计中的潜力》

The Potential of Machine Learning for Hardware Design

在这次演讲中,我将描述机器学习在过去十年中取得的巨大进步,它如何改变了我们想要用来执行计算的硬件,并描述一些潜在的领域,使用机器学习来帮助解决计算机硬件设计中的一些困难问题。我还将简要介绍机器学习的一些未来方向,以及它可能如何影响未来的事情。

https://www.dac.com/Conference/2021-Keynote-Speakers

第一天, Google大神、Google AI的领导人Jeff Dean,进行了题为"机器学习在硬件设计中的潜力"的主题演讲。近年来,谷歌研究了不少深度学习在EDA方面的应用,其中最著名的是他们去年发表在Nature上的工作,通过强化学习自动进行macro placement,并真正应用于Google的硬件加速器TPU的设计过程。

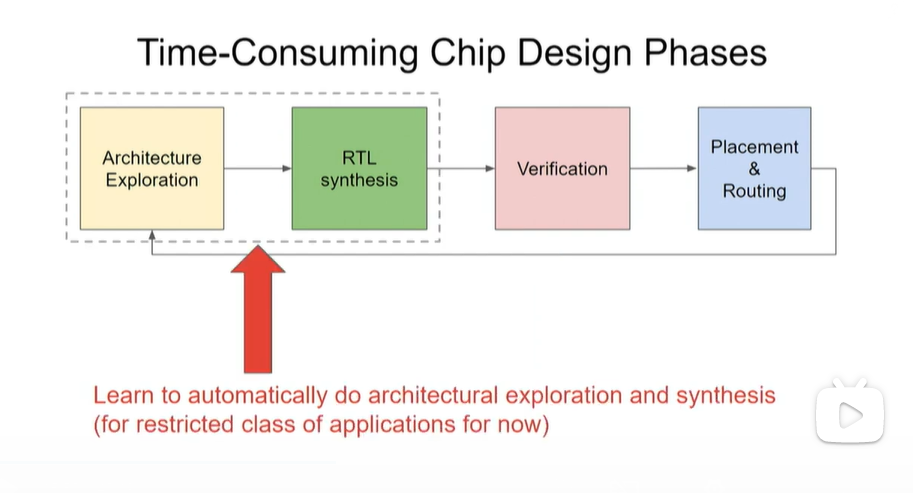

Jeff在演讲中提到了Google使用深度学习优化整个芯片设计流程的工作,主要分为三个部分,对于芯片设计的三个主要阶段。如下图所示,演讲包括使用深度学习加速1.架构搜索和RTL综合,2. 验证,3. 芯片布局绕线。

在架构搜索阶段,Google提出了叫做FAST的架构自动对硬件加速器的设计进行优化,他们使用了Google自己的黑盒优化器Vizier进行搜索。对于验证阶段的工作,Google提出了使用图神经网络(GNN)对RTL阶段的芯片设计进行分析处理。对于布局布线部分,重点自然就是发表在Nature的macro placement工作。

正式Keynote结束后,我们也和Jeff就ML for EDA进行了讨论。Jeff肯定了现有的商业EDA工具的表现。当我们问到在EDA方面,是否直接生成结果的强化学习方法将会取代仅进行预测的ML模型时,他认为两者在未来都将发挥重要作用。

在过去的十年中,系统和硬件已经改变了机器学习。现在是机器学习改变系统和硬件的时候了。在芯片设计过程中,芯片布局(chip placement)可以说是其中最复杂和耗时的步骤了。芯片设计周期的缩短有助于硬件设备适应机器学习领域的快速发展,那么,机器学习能否助力芯片设计呢?最近,谷歌提出了一种基于强化学习的芯片布局方法。本报告内容包括:

学习优化器件放置

学习配分图

学习优化芯片布局

博客链接:http://ai.googleblog.com/2020/04/chip-design-with-deep-reinforcement.html

论文链接:https://www.nature.com/articles/s41586-021-03544-w

在芯片设计过程中,芯片布局(chip placement)可以说是其中最复杂和耗时的步骤了。芯片设计周期的缩短有助于硬件设备适应机器学习领域的快速发展,那么,机器学习能否助力芯片设计呢?最近,谷歌提出了一种基于强化学习的芯片布局方法。

专知便捷查看

便捷下载,请关注专知公众号(点击上方蓝色专知关注)

后台回复“MLHD” 就可以获取《Google大神Jeff Dean最新DAC演讲《机器学习在硬件设计中的潜力》》专知下载链接