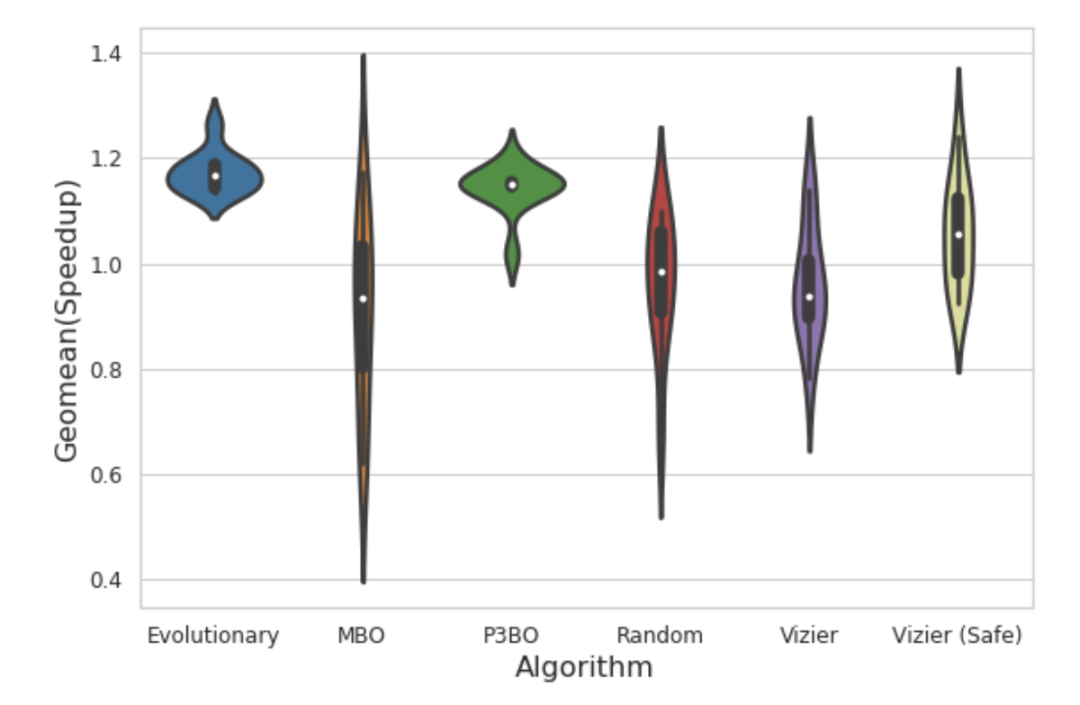

用Apollo设计芯片!Google说懂芯片才能更快「炼丹」

新智元报道

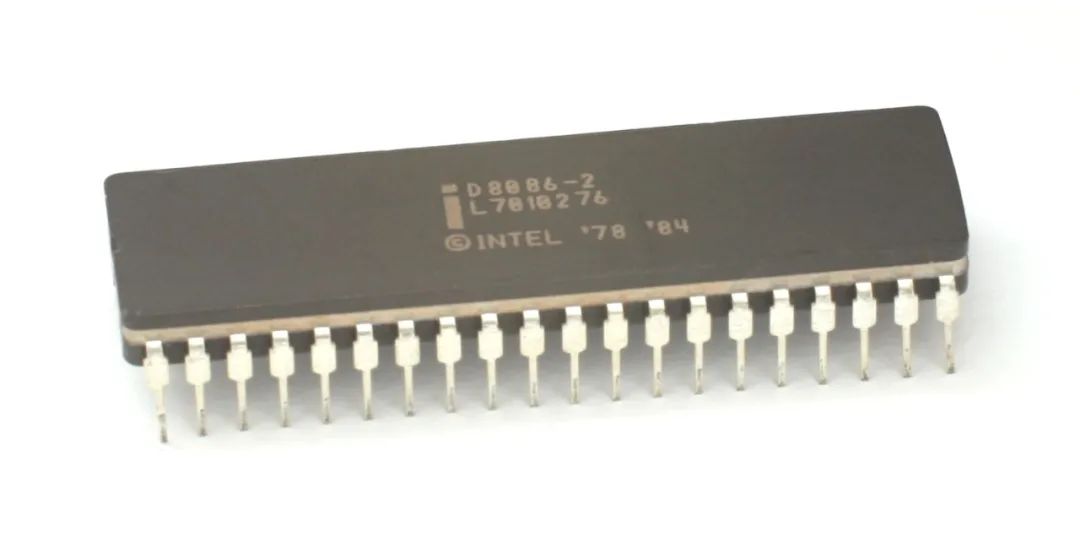

【新智元导读】「在某些情况下,深度学习能够比人类做出更好地设计芯片电路」,Jeff Dean如是说。

登录查看更多