晶体管救命稻草来了:3D堆叠CMOS,摩尔定律又续10年?

新智元报道

新智元报道

【新智元导读】3D堆叠CMOS将是把摩尔定律延伸到下一个十年的关键。

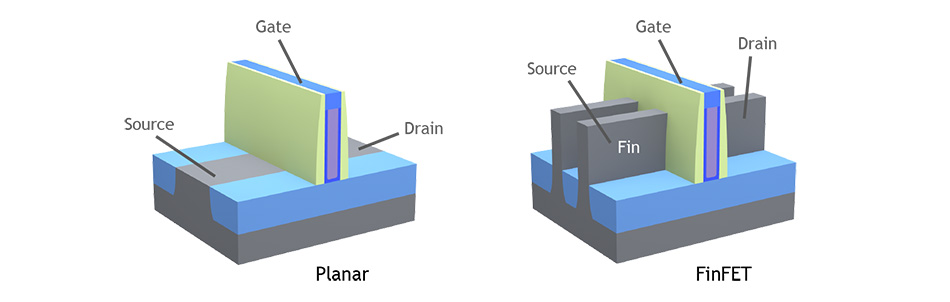

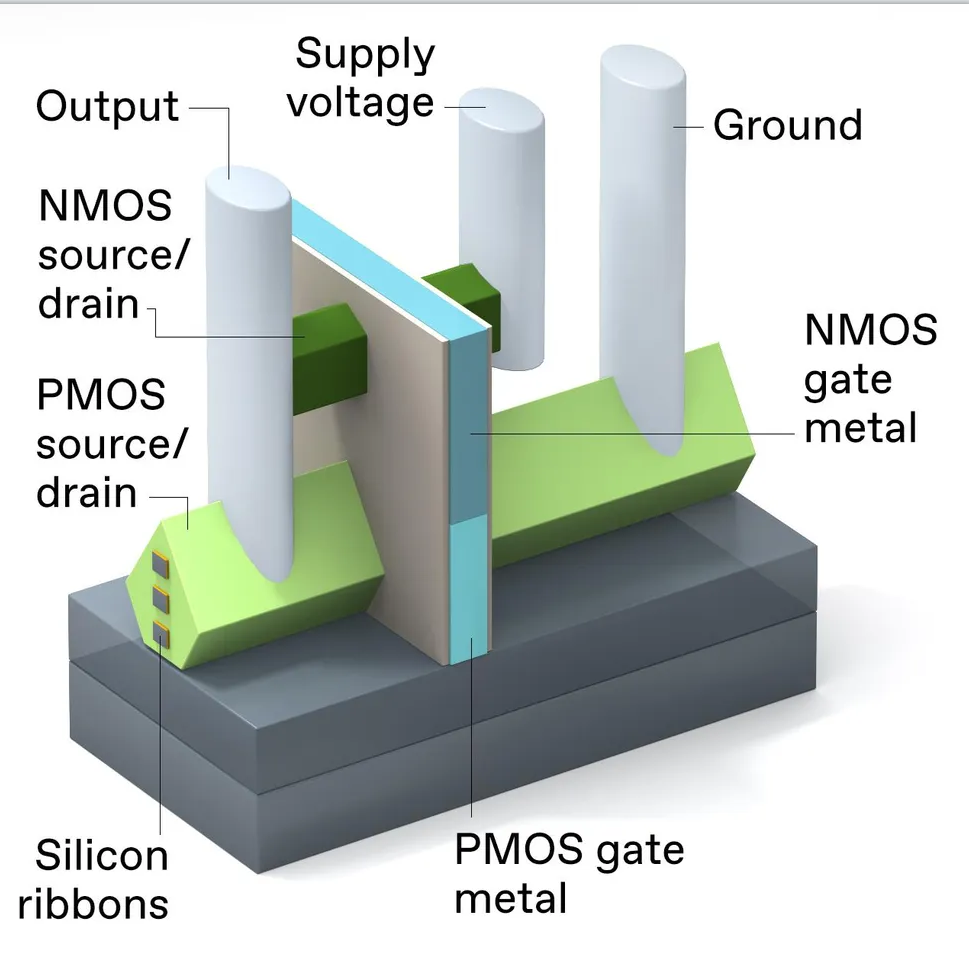

晶体管的演变

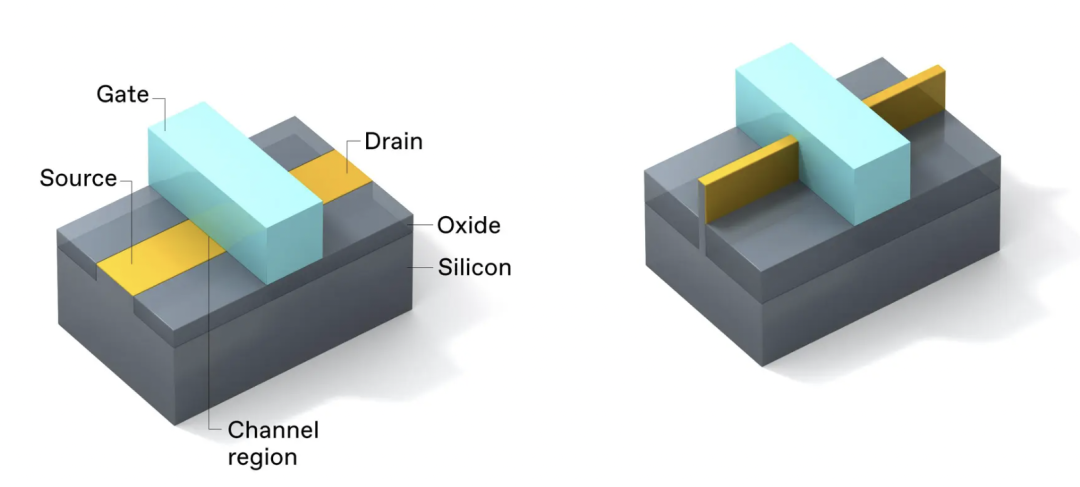

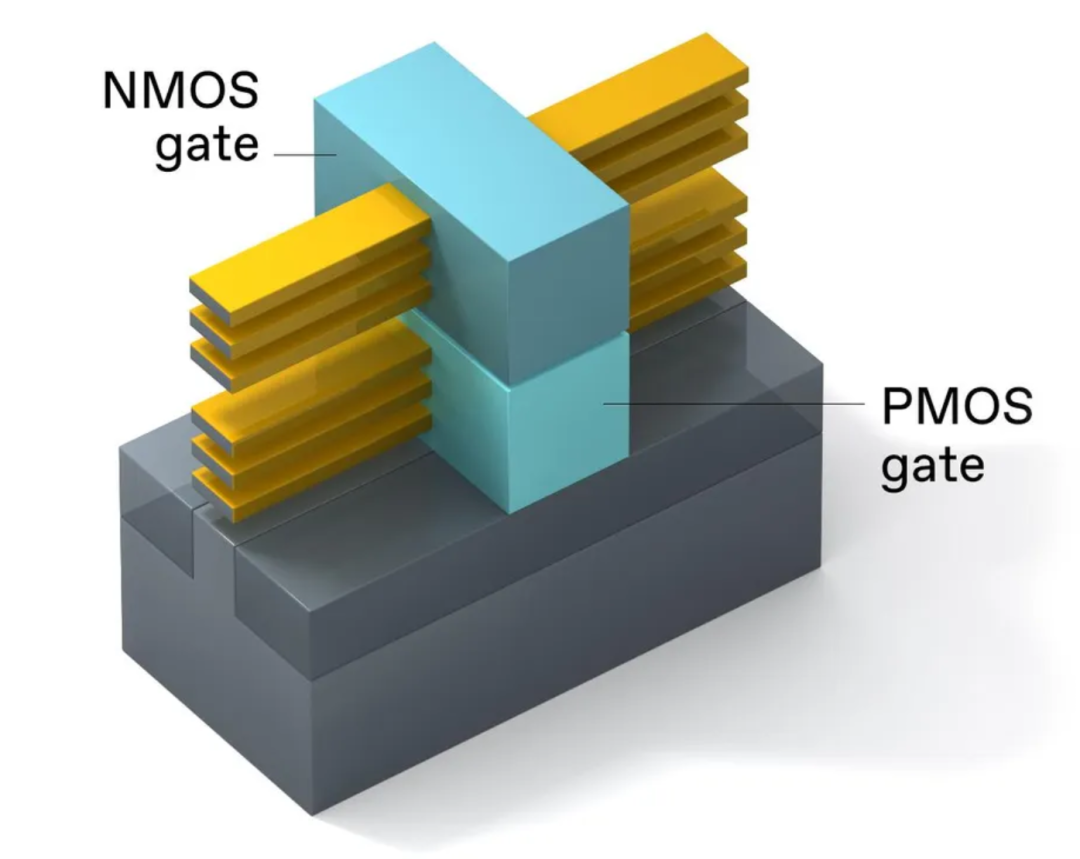

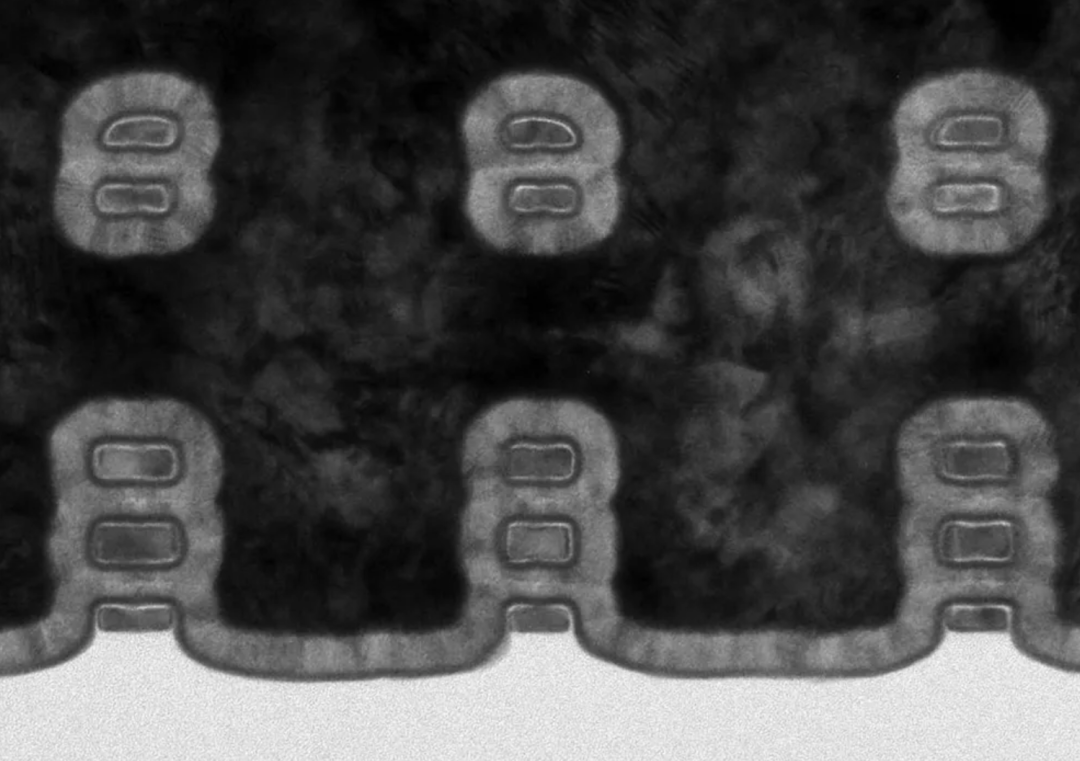

3D堆叠CMOS

摩尔定律的未来

登录查看更多

相关内容

Arxiv

0+阅读 · 2022年11月24日

Arxiv

13+阅读 · 2018年3月1日