清华团队率先抵达摩尔定律最后节点,0.34nm栅长晶体管研究登Nature,打破斯坦福纪录

晓查 发自 凹非寺

量子位 | 公众号 QbitAI

晶体管到底能做到多小?最近清华大学集成电路学院任天令教授团队给出了答案。

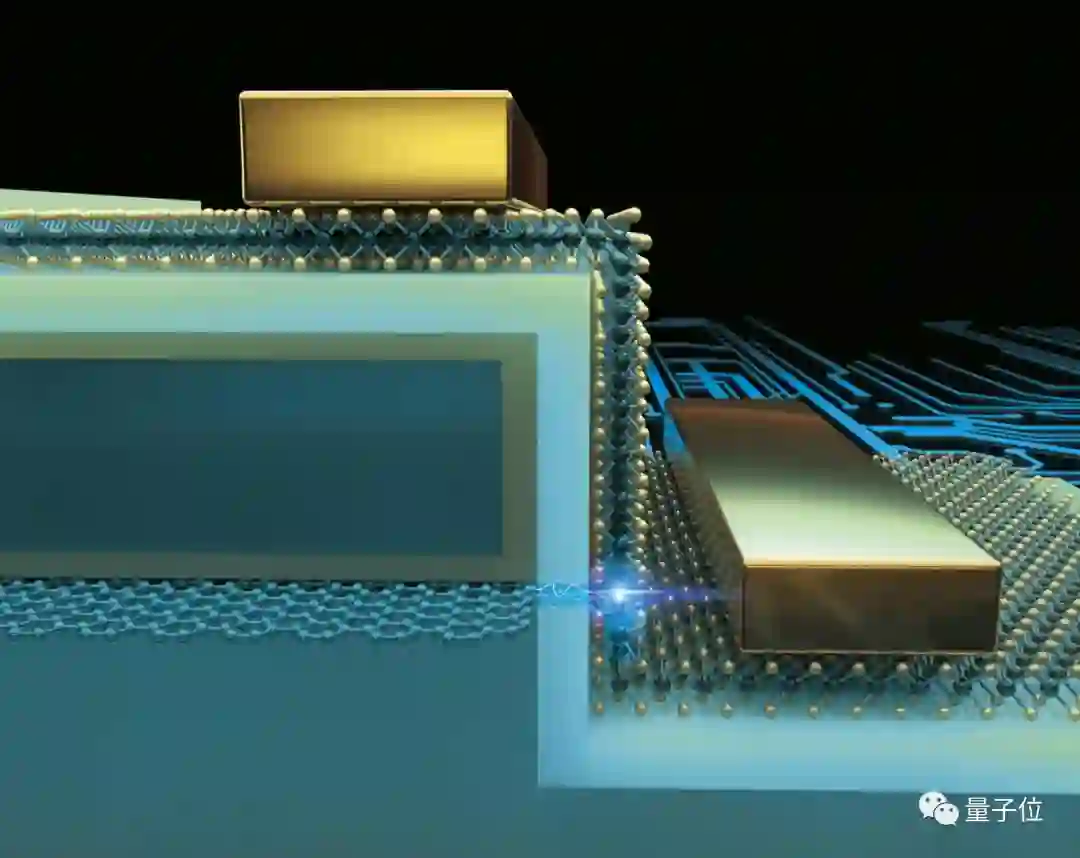

该团队以单层石墨烯作为栅极,打造出一种“侧壁”晶体管,创下了0.34nm栅极长度的纪录,这项研究登上了最新一期Nature。

2016年由斯坦福大学用碳纳米管造出1nm栅极长度晶体管,6年后纪录终于被打破。

任天令指出,这可能是摩尔定律的最后一个节点。

在未来,人们几乎不可能制造小于0.34 nm的栅极长度。

那么,清华大学团队的侧壁晶体管到底有何特别之处?

侧壁晶体管

我们先介绍一下晶体管的基本原理。

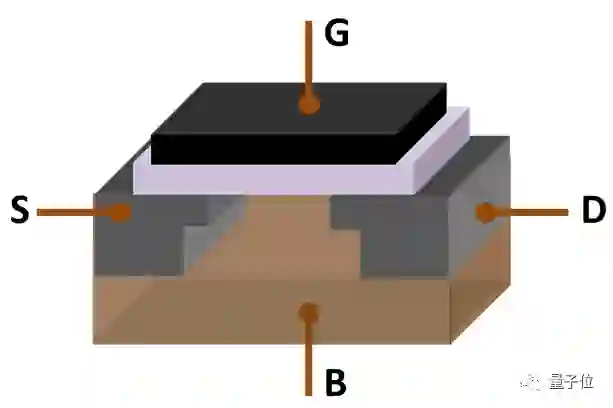

现代芯片中的基本单元晶体管,更准确地说是场效应管(MOS)包括源极(Source)和漏极(Drain)两个导电电极,中间由一块半导体隔开。

源极和漏极之间是否能导通,全由栅极(Gate)来控制。而栅极长度是衡量晶体管尺寸的最重要指标之一。

为了在一块芯片中塞入更多晶体管,必须减小晶体管尺寸,尤其是栅极尺寸。

例如现在用于5nm制程的FinFET,就是将栅极竖起来,减小单个晶体管面积。

2016年,斯坦福大学用单壁碳纳米管制成栅极,做到了1nm,研究成果登上了Science。

如何让栅极长度进一步减小呢?比碳纳米管还薄的单层石墨烯片可以。它的厚度只有一个碳原子大小——0.34nm。

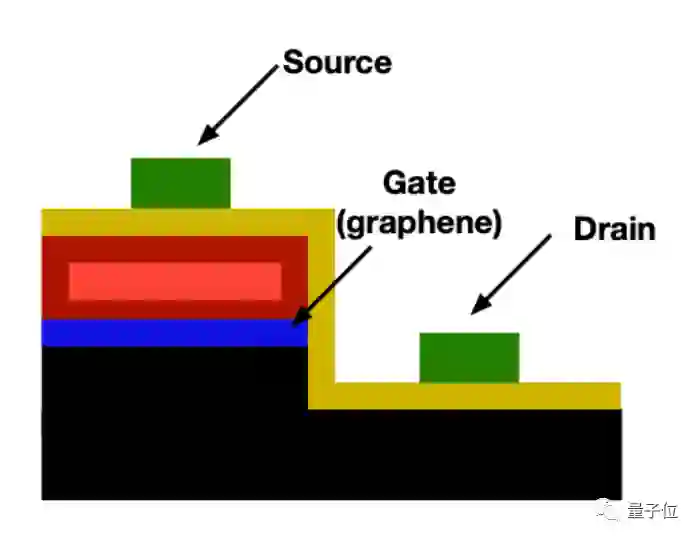

为了制造这种晶体管,研究人员重新设计了晶体管的结构。

△ 侧壁晶体管的结构示意图

首先将石墨烯沉积在二氧化硅基底上,再在石墨烯表面沉积一层金属铝。虽然铝是一种导体,但研究人员让它在空气中放置几天,表面形成氧化铝。

这样石墨烯的下面是二氧化硅,上面是氧化铝,与上下层都绝缘。

然后,研究人员沿着铝的边缘向下蚀刻到二氧化硅层中,露出石墨烯的边缘,以此作为只有一个原子厚的栅极。

△ 侧壁晶体管的工艺流程

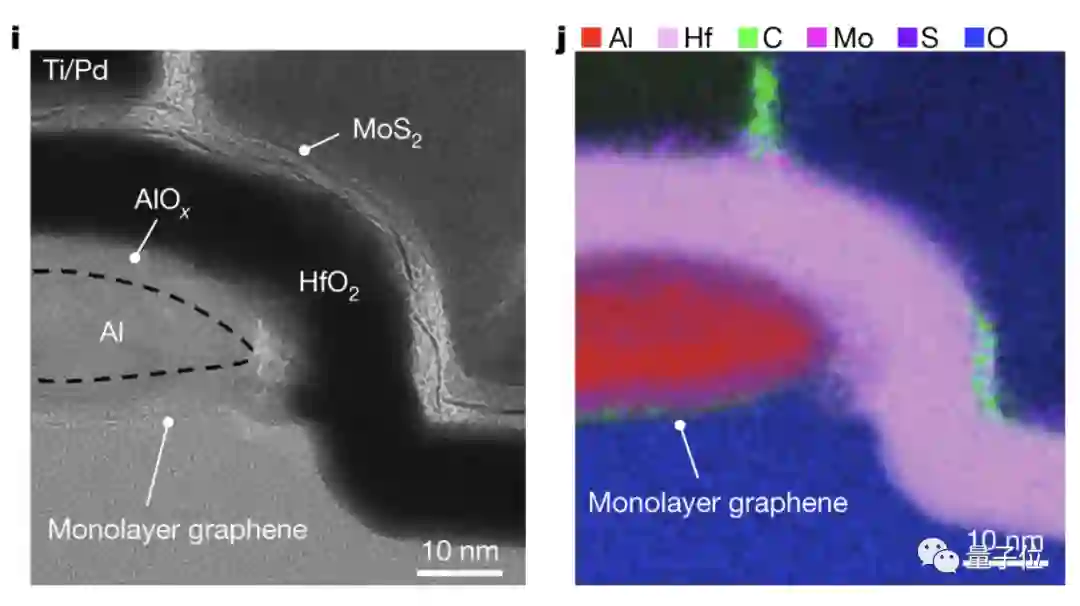

整个器件表层先被一层薄薄的氧化铪绝缘层覆盖,再加上一层二硫化钼半导体作为源极和漏极之间的沟道。

由钛钯金属制成的源极和漏极,分别放置在栅极的两侧,它们中间有一道垂直墙,因此被叫做侧壁(Sidewall)晶体管。

△ 侧壁晶体管的显微结构

研究发现,由于单层二维二硫化钼薄膜相较于体硅材料,具有更大的有效电子质量和更低的介电常数,在亚1纳米物理栅长控制下,晶体管能有效的开启、关闭,其关态电流在pA量级。

由于这种晶体管的漏电流很小,因此可用于低功率操作。

但是现在制作侧壁晶体管的过程还比较复杂,研究人员只造出了数十个晶体管,距离实用化还有很长的路要走。

团队简介

本文通讯作者为清华大学集成电路学院任天令教授和田禾副教授。

清华大学集成电路学院2018级博士生吴凡、田禾副教授、2019级博士生沈阳为共同第一作者。

△ 任天令教授与田禾副教授

任天令,1997年博士毕业于清华大学现代应用物理系,2003年起担任清华大学微电子所教授,主要研究方向为智能微纳电子器件、芯片与系统。

田禾,2015年博士毕业于清华大学,导师为任天令,现为清华大学微电子所、集成电路学院副教授,博士生导师。

参考链接:

[1]https://www.nature.com/articles/s41586-021-04323-3

[2]https://arstechnica.com/science/2022/03/a-transistor-made-using-two-atomically-thin-materials-sets-size-record/

[3]https://spectrum.ieee.org/smallest-transistor-one-carbon-atom

[4]https://www.tsinghua.edu.cn/info/1175/92075.htm

[5]https://www.sic.tsinghua.edu.cn/info/1015/1035.htm

— 完 —

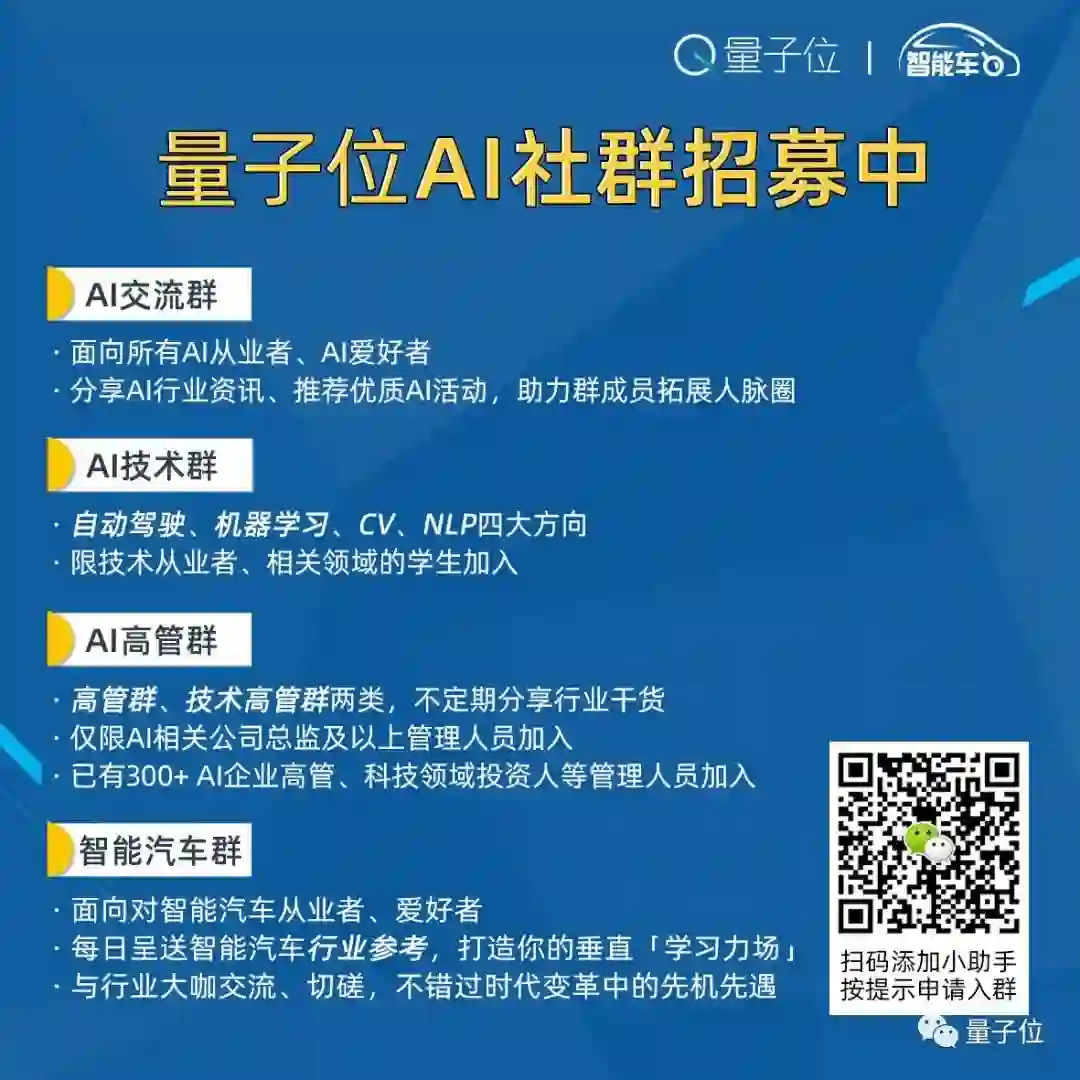

「人工智能」、「智能汽车」微信社群邀你加入!

欢迎关注人工智能、智能汽车的小伙伴们加入我们,与AI从业者交流、切磋,不错过最新行业发展&技术进展。

ps.加好友请务必备注您的姓名-公司-职位哦~

点这里👇关注我,记得标星哦~

一键三连「分享」、「点赞」和「在看」

科技前沿进展日日相见~