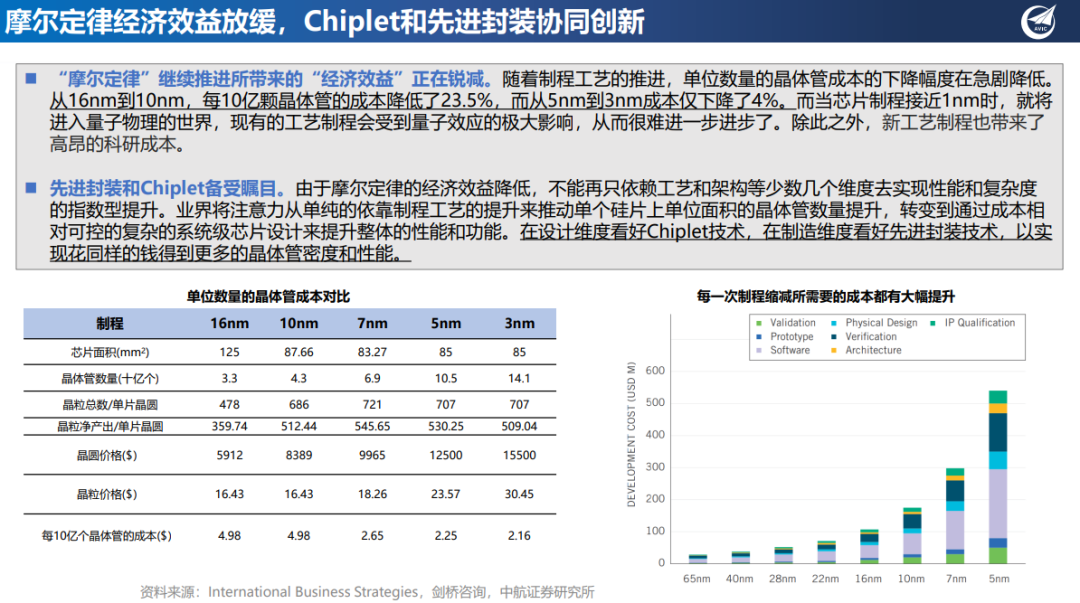

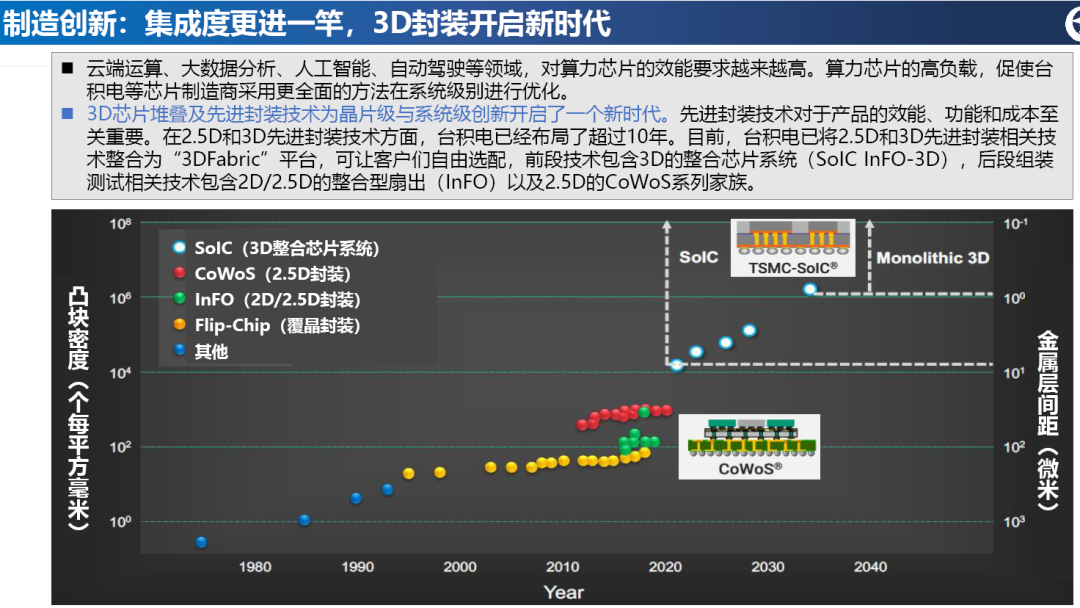

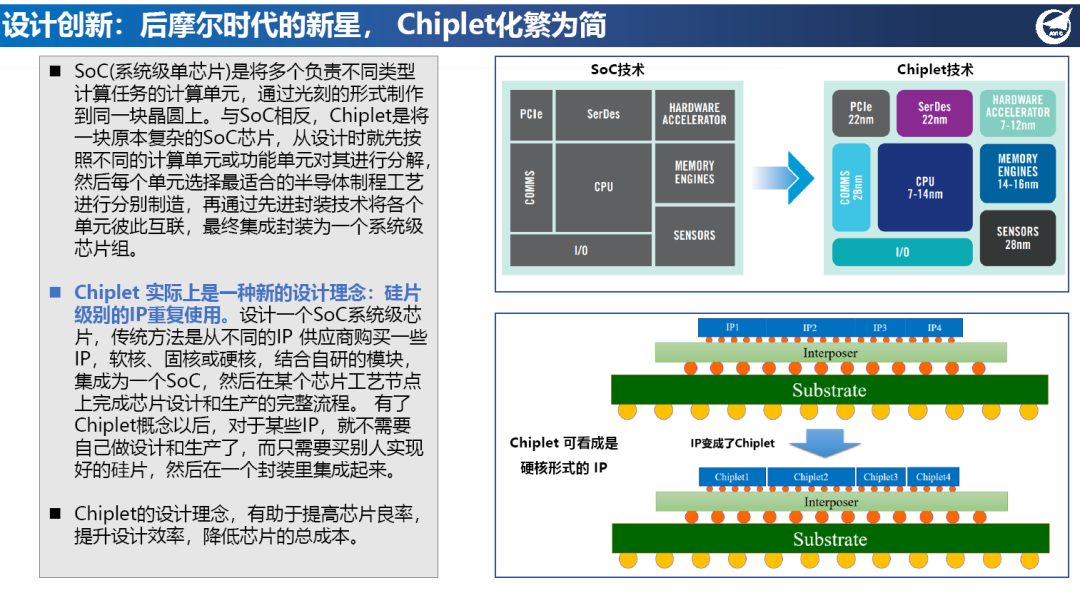

摩尔定律经济效益放缓,Chiplet和先进封装协同创新:由于摩尔定律的经济效益降低,不能再只依赖工艺和架构等少数几个维度去实现性能和复杂度的指数型提升。业界将注意力从单纯的依靠制程工艺的提升来推动单个硅片上单位面积的晶体管数量提升,转变到通过成本相对可控的复杂的系统级芯片设计来提升整体的性能和功能。在设计维度看好Chiplet技术,在制造维度看好先进封装技术,以实现花同样的钱得到更多的晶体管密度和性能。 Chiplet将设计化繁为简,降本增效:Chiplet是一种新的设计理念:硅片级别的IP重复使用。设计一个SoC系统级芯片,传统方法是从不同的IP供应商购买一些IP,软核、固核或硬核,结合自研的模块,集成为一个SoC,然后在某个芯片工艺节点上完成芯片设计和生产的完整流程。有了Chiplet概念以后,对于某些IP,就不需要自己做设计和生产了,而只需要买别人实现好的硅片,然后在一个封装里集成起来。Chiplet的设计理念,有助于提高芯片良率,提升设计效率,降低芯片的总成本。 先进封装是实现Chiplet的前提:Chiplet对先进封装提出更高要求。在芯片小型化的设计过程中,需要添加更多I/O来与其他芯片接口,裸片尺寸有必要保持较大且留有空白空间,导致部分芯片无法拆分,芯片尺寸小型化的上限被pad(硅片的管脚)限制。并且,单个硅片上的布线密度和信号传输质量远高于Chiplet之间,要实现Chiplet的信号传输,就要求发展出高密度、大带宽布线的“先进封装技术”。 Chiplet新蓝海,国产设计大机遇:Chiplet发展涉及整个半导体产业链,将影响到从EDA厂商、晶圆制造和封装公司、芯粒IP供应商、Chiplet产品及系统设计公司到Fabless设计厂商的产业链各个环节的参与者。在芯片设计端,建议关注国内平台化的IP供应龙头芯原股份,积极布局2.5D封装技术的国芯科技,以及国内EDA供应商华大九天、概伦电子、安路科技、广立微。