作者:马恺声

编辑:好困

【新智元导读】Chiplet最近可谓是风口正劲,但是芯片行业并不是简简单单比拼谁能做出来就可以的。

Chiplet需要通过大规模量产催动行业更新,同时还要考虑产品良率、封装良率、各种成本等等。

在这个前提下,只有折算下来的好处能够明显超过传统soc方案,才能够被非常好的推广。

文中数据皆真实可考,一部分获取于2021年作者自己的芯片加工与封装等,一部分借助于Chiplet产业联盟所获取。

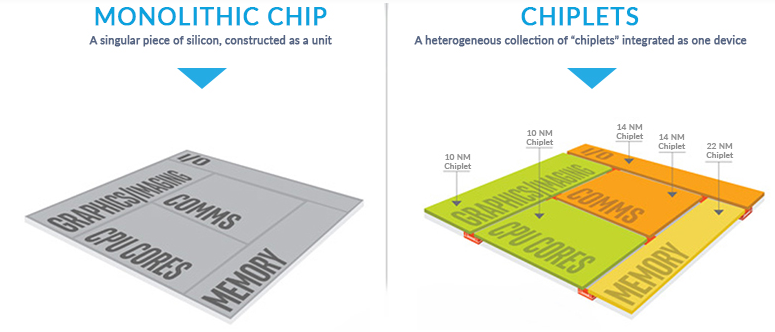

多芯片集成技术被业界广泛认为是摩尔定律的延续,节省成本是其广为人知的优势之一,但是很少有工作能够定量地展示多芯片集成系统对比单芯片的成本优势。

我们基于三种典型的多芯片2.5D集成技术,建立了一个定量的多芯片系统成本模型,并提出了一套分析方法,从良品率提高、芯片和封装复用以及异构集成等多方面分析了多芯片系统的成本效益。

文章被Design Automation Conference(DAC)2022录用。清华交叉院博士研究生冯寅潇是该论文的第一作者,清华大学交叉院助理教授马恺声是该论文的通讯作者。

论文链接:https://doi.org/10.48550/arXiv.2203.12268

与传统的单芯片系统相比,多芯片集成系统的成本计算变得更加复杂,如果不经过认真评估,盲目采用多芯片架构反而会导致更高的成本。

因此,我们建立一个名叫「Chiplet精算师」的成本模型,利用此模型对多芯片集成系统的成本效益进行了精致的评估,并回答了架构设计者所面临的诸多难题:

该采用何种封装集成方案?

该把整个系统拆成多少小芯片?

是否应该在多个系统间复用封装?

如何复用芯片?

-

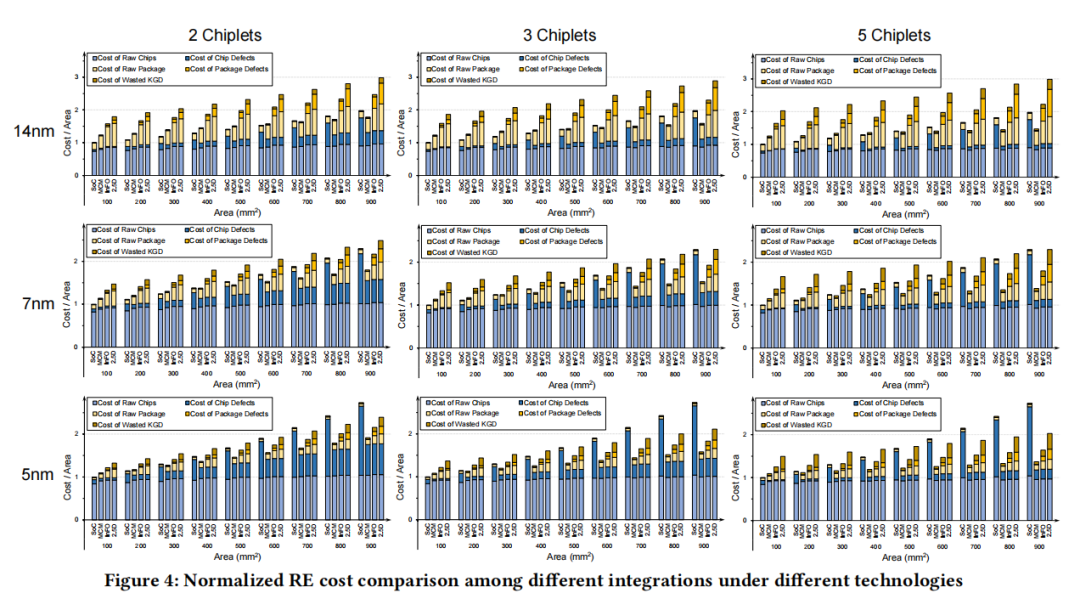

1. 不是所有的芯片在经济上都适合用Chiplet技术。

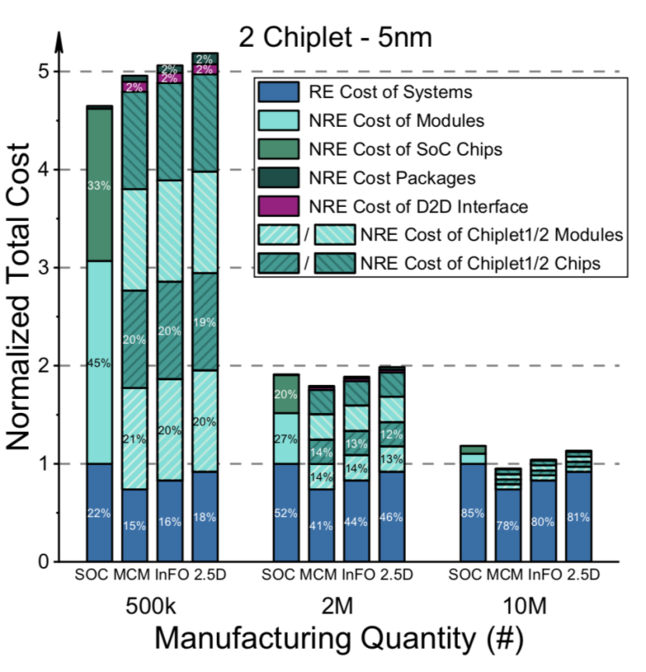

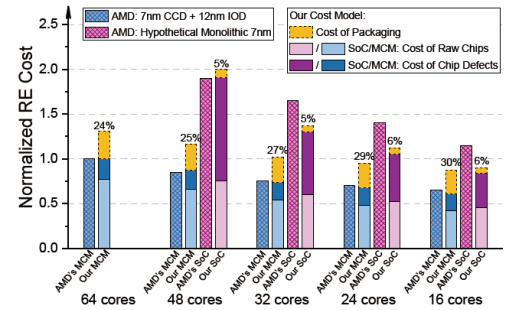

这张图中的9个柱状图,都是RE Cost(recurring engineering cost,可以理解成不考虑一次性投入,生产一片芯片的钱),横向是14nm,7nm,5nm,纵向是几个Chiplets封装到一起。

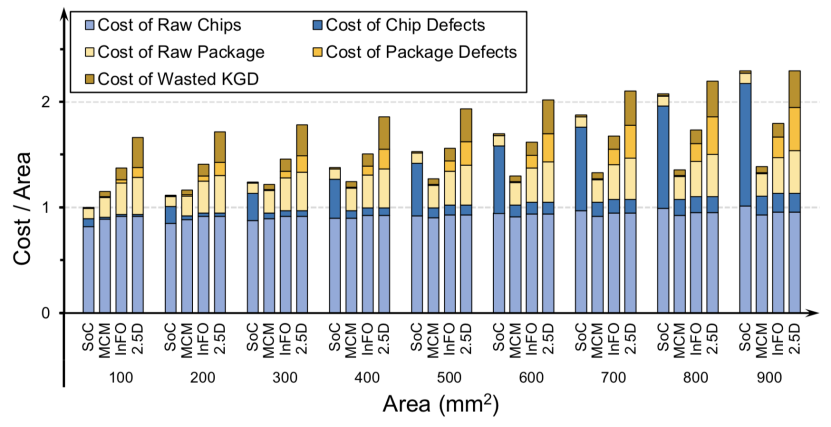

我们再看一个详细的图,是上图中7nm,5个Chiplets拼一起放大版。图的横轴是面积,纵轴是单位面积成本。四种封装方式为:SoC,MCM封装,InFO,2.5D封装。

可以看到,如果在200平方毫米以下,没有必要做Chiplet。真正有收益的时候在800平方毫米以上的大芯片。这也是为什么今天超大的芯片用Chiplet方案,因为经济上确实是更合适的。

另外,伴随先进封装而来的大量测试、封装成本,极其先进的封装都非常昂贵,甚至数倍于硅的成本,首要解决的是能不能做大芯片的问题。未来随着封装价格的下降,Chiplet路线会越来越有收益。

MCM和InFO成本相对更低,更划算,预计基于先进封装里面的基础封装的芯片会更早起量。

2. 多芯片集成在越先进工艺下(如5nm)越具有显著的优势,因为在800

mm2

面积的单片系统中,硅片缺陷导致的额外成本占总制造成本的50%以上。

对于成熟工艺(14nm),尽管产量的提高也节省了高达35%的成本,但由于D2D接口和封装开销(MCM:>25%,2.5D:>50%),多芯片的成本优势减弱。

3. 虽然制造成本是需要考虑的主要成本,但一次性投入的成本往往是决定性的,特别是对于没有巨大产量保障的产品。

对于单个系统,我们发现,单独做每个小芯片,都存在很高的一次性投入成本,如流片时掩膜板的成本,因此多芯片架构导致总的一次性投入成本非常高(50万产量时占到总成本的36%)。对于5nm系统,当产量达到2千万时,多芯片架构开始带来回报。

也就是说,如果单一企业想要靠着自研全部的小芯片来搭建芯片,并且只有一款芯片的话,并不划算。但是确实能带来比如高中低档次芯片的搭配等优势。

当然,这里面一次性投入成本可以伴随着小芯片的复用,得到巨大的收益。

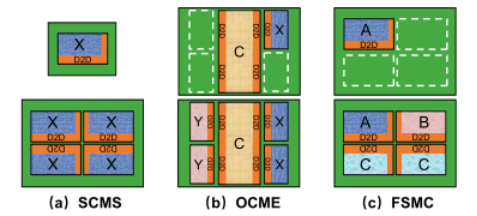

通过许多探究实验发现,多芯片架构的成本优势需要通过充分利用复用和异构来实现。把常见的多芯片复用架构分为三类:单芯片多系统(SCMS)、一中心多拓展(OCME)和固定插座多组合(FSMC)。

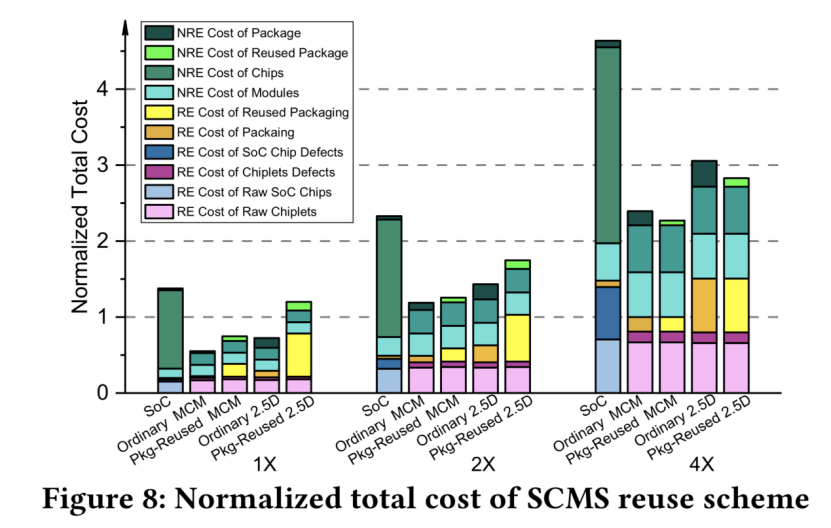

1. 对于SCMS架构,由于芯片复用,与单芯片系统相比,芯片大量节省了一次性投入成本。

该复用方案的最大优点是只需要一个芯片,因此无需制造多个芯片可立即生效,这种架构适用于同一产品线不同等级的产品。(镜像Die在设计制造过程成本在这里被当做单个Die来考虑,影响方案,不影响成本核算。谢谢夏晶指出)

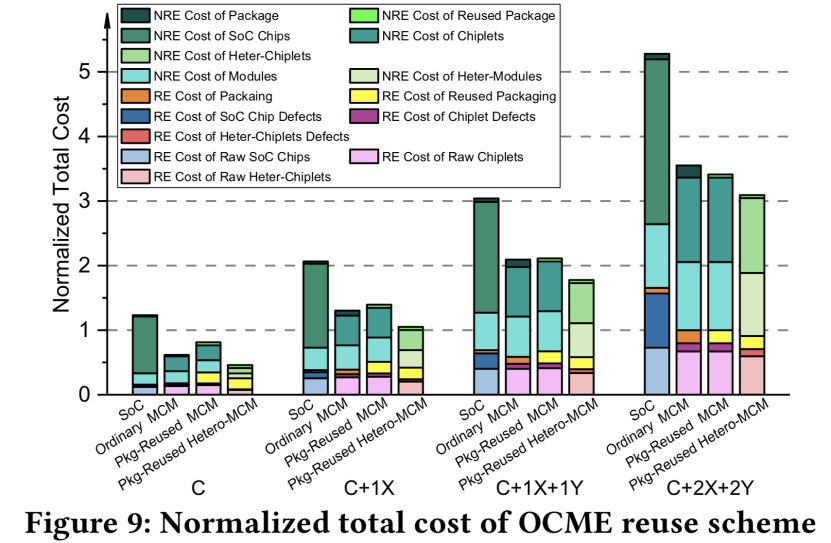

2. OCME架构相比SCMC,使得异构工艺成为可能。

如果把多个系统共用的对先进工艺不敏感的模块坐在落后工艺的中心硅片上,可以带来巨大的收益,许多包含了DDR、PCIe等模块的系统都可以采用此架构。

数据中的Pkg-reused的概念是封装复用,比如一个基板上可以放4个,实际上只放了2个Die,另外两个Die用Dummy Die填充以解决散热和应力问题。那这样封装看起来并不是最大化利用的,但是总体来看,反而更加划算了。

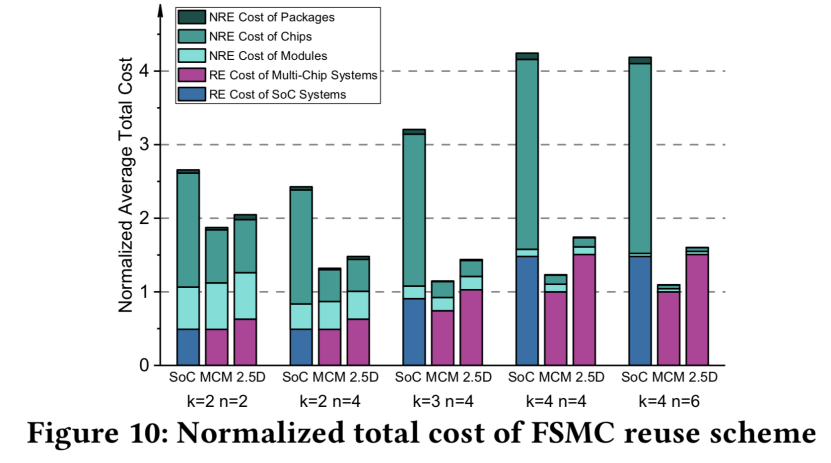

3. 对于FSMC架构,则是把复用可能性最大化了。

复用的芯片越多,一次性投入成本摊销的收益就越大。

当可复用性得到充分利用时,均摊后的先期投入就会小到可以忽略。在这一点上,多芯片架构的巨大成本节约潜力便显现出来。

成本优势不仅体现在制造成本的节约上,也体现在一次性投入成本的节约上。看得出来,到了最后,谁的手里有更多的Die,或者说谁的方案能兼容更多的Die,谁就能更多节省成本。

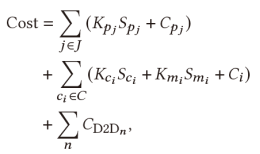

图中k是Package上面有多少个Slot,n是手里有多少种不同的Die

当然了,多芯片架构的优势不是无条件的,而是取决于许多复杂的因素。

为了帮助芯片架构师在多芯片架构上做出更好的决策,我们建立了一个定量模型来比较不同方案的成本。

模型允许设计师在早期阶段验证成本。我们还展示了多芯片体系结构如何从良率提高、芯片和封装复用以及异构性中获益:

当硅片缺陷的成本超过封装导致的成本时,多芯片架构开始带来回报。

系统越接近摩尔极限(最先进工艺,最大面积),多芯片架构的成本效益就越高。

更小的芯片粒度带来的成本效益具有边际效应,所以,把单独一个IP做成一个Die是不划算的。

是否复用封装取决于制造成本和均摊的一次性投入成本哪个占主导地位。量小的时候,要尽量的复用封装;量多的时候,可以单独再次开发先进封装。这个平衡点大约在80-100万颗每年。

对于档次分明的同质系统,SCMS方案具有显著的成本优势;对于共享大面积HUB模块的系统,采用OCME方案更具成本效益;FSMC方案提供了最大的复用可能性,但是对Die的形状,以及四边的接口数量要求很高。

基本原则是用更少的芯片构建更多的系统,芯片复用的成本效益对于破碎化、层次化的需求更为明显。

站在今天的角度看:先进封装,并不是越先进越好,价格过高,数倍于硅的成本,决定了其不会大范围量产使用;反而是,基本版本的先进封装在性能上基本上可以满足架构诉求,可能会最先被大范围使用。提高良率、降低成本是国内封装厂的要务(尤其是在基板生产方面)。从未来的角度看,据我们所知,国内有接近十家基板厂商在建设,数家先进封装厂在建设,按照两年建厂,两年良率爬坡的发展节奏,未来三四年后,先进封装良率和成本将迎来大幅优化。到时候,Chiplet技术应用将迎来规模性爆发。

机会仍在,国内同仁仍需努力!

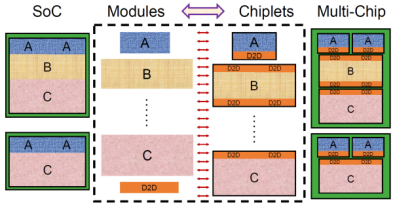

Chiplet精算师引入了模块、芯片和封装三个概念,任何一个系统都可以由这三个层次构成。

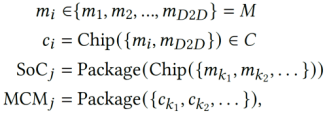

其中,每个Chiplet对应一个模块,D2D接口作为一个特殊的模块在多个Chiplet间复用,可以用数学语言表达为:

芯片的制造成本可以大致分为:

(1)硅片成本,(2)硅片缺陷导致的损失,(3)封装成本,(4)封装缺陷导致的损失,以及(5)封装缺陷所导致好硅片的浪费。

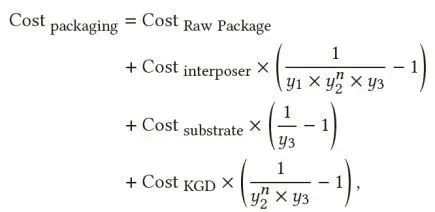

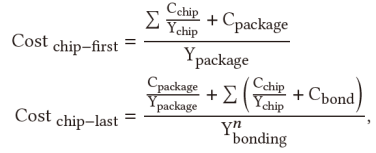

(1)(2)两项在前人的工作中已经被充分讨论,与多芯片集成和先进封装相关的(3)(4)(5)成本可以表达为:

其中,y1是中间插入层制造的良率,y2是芯片与插入层键合的良率,y3是中间插入层与基板键合和良率。与此同时,chip-first与chip-last两种不同的封装工艺流程也被考虑在内:

一次性投入成本(NRE,包括软件与IP授权、系统设计验证以及流片费用等)占据了总成本的一大部分。

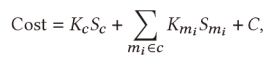

我们从面积入手,在成本模型中引入了一次性投入成本。对于任何一个芯片,其一次性投入成本可以估计为:

其中

Sc

是芯片的面积,

Sm

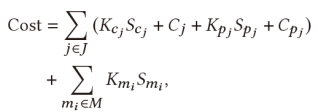

是模块的面积,C是与面积无关的固定投入。由此可以得到如果要设计若干套系统,如果均采用单芯片架构,总的一次性投入成本可以估计为:

而如果采用多芯片架构,总的一次性投入成本可以估计为:

其中,

Sp

是封装面积,

Cp

是封装的固定投入,

CD2D

是开发D2D接口的投入。

KmSm

:与模块面积相关的NRE成本,包括模块前端设计、模块前端验证等。

KcSc

:与芯片面积相关的NRE成本,包括架构设计、系统验证、后端设计、后端验证等。

C:与芯片和模块面积无关的NRE成本,包括软件授权、IP授权、流片(芯片试制的掩膜费用)等。

KpSp

:与封装面积相关的NRE成本,包括封装设计等。

Cp

:与封装面积无关的NRE成本,包括封装制造开模等成本。

其他开销,比如设备费、场地费、日常维护费用视情况包含于C或

KcSc

。

这个成本模型在AMD的多芯片架构上进行了验证,在硅片成本上,取得了与AMD公开数据基本一致的结果。

区别在于AMD没有算入先进封装集成多块芯片的额外成本。

马恺声:清华大学交叉信息研究院教研系列助理教授。

![]()

他在宾夕法尼亚州立大学计算机科学与工程系获得博士学位。研究重点是计算机结构、计算机视觉相关人工智能算法设计,重点是可解释、稳健性和紧凑模型设计。

他在CVPR、NeurIPS等AI会议,DAC、ISCA等计算机体系结构会议发表文章。并曾获得过诸多奖项,包括2015年HPCA最佳论文奖,2016年IEEE MICRO Top Picks,2017年ASP-DAC最佳论文奖。2018年EDAA最佳博士论文奖。

此外,他还获得了2016年宾夕法尼亚州立大学CSE系最佳研究生研究奖,2016年NSF ASSIST工程研究中心通讯封面特写,2011年杨芙清-王阳元院士奖学金。

他是清华大学交叉信息研究院的在读博士生(博士二年级),导师为马恺声。

他本科毕业于上海交通大学,获信息工程(人工智能方向)和数学与应用数学双学位。同时,他也是上海交通大学致远工程荣誉项目的成员。

本科期间,他获得了许多与众不同的奖项和荣誉,包括国家奖学金。他在材料、器件、电路、算法和硬件方面具有混合背景和经验。他甚至有无尘室制造的经验。

参考资料:

https://doi.org/10.48550/arXiv.2203.12268

![]()

![]()