低成本有源相控阵天线研究

来源 | 射频百花潭

作者 | 何庆强

研究了有源相控阵天线的低成本设计思路和数字技术新方法。首先详细地分析了有源相控阵天线的系统构架和成本组成; 然后从系统总体的角度,探讨了低成本数字阵列相控阵天线设计方法; 最后提出了采用宽带宽角扫描的可重构设计技术来降低有源相控阵天线的成本。提出的有源相控阵天线低成本设计新方法具有很好的工程实用价值和科学意义。

s频段高动态宽角度数字多波束相控阵天线

有源相控阵天线低成本设计方法是电子扫描天线发展的重要方向,也是相控阵天线形成系列化产品的重要前提。在低成本电子扫描天线方面,国内外大部分文献报道了透镜体制相控阵天线的低成本设计方法[1-6],该相控阵天线波束扫描采用铁氧体移相器技术,将经典二维扫描相控阵天线的移相单元数由M×N 个减少到M+N 个,大大降低了相控阵天线的成本。但这种非有源相控阵天线的设计方法会使相控阵天线体积增大,不利于列装空天飞行器平台,同时这种透镜相控阵天线也存在着较大的缺陷:铁氧体移相器行/列相位控制结构非常简单,导致所有行/列的单元通道上的相位都相关,这不利于用波束控制系统来校正单个移相器通道的误差,从而会恶化旁瓣电平,降低波束指向精度; 而将移相器数量大幅减少,这意味着一旦某个移相器失效,则单元的所有行或列均会不工作,从而导致相控阵天线无法正常运行。

此外,其他减少有源相控阵天线成本的方法国内外也有报道[7-10],这些方法虽然降低了成本,但同时也牺牲了相控阵天线的指标性能,尤其是波束扫描的灵活性和波束捷变的能力,难以满足宽角宽域扫描的需求。总之,目前国内外文献提出的低成本天线设计方法要么采用体积大的透镜体制,要么牺牲部分天线功能的折中方案。

随着动中通业务的快速发展、5G 通信和物联网技术的兴起,高数据率和全空域覆盖成为通信技术发展的重要目标,一体化、高性能、低成本有源相控阵天线的宽角扫描能力和波束捷变能力优势明显,越来越显示出巨大的潜力,成为有源相控阵天线发展的一个重要方向[11-12]。本文针对国内外相控阵天线低成本设计方法的不足之处,从实际工程应用出发,提出了新的有源相控阵天线低成本设计方法,该新方法能够指导系统工程总体设计和产品研制,具有很好的科学意义和实用价值。

系统架构研究

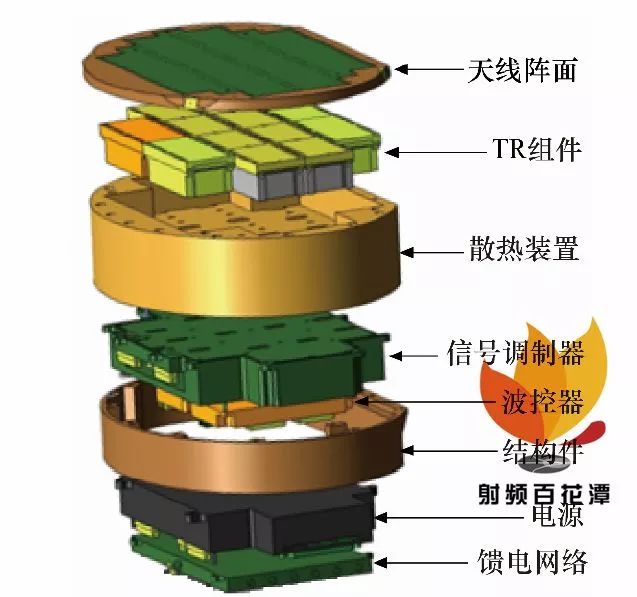

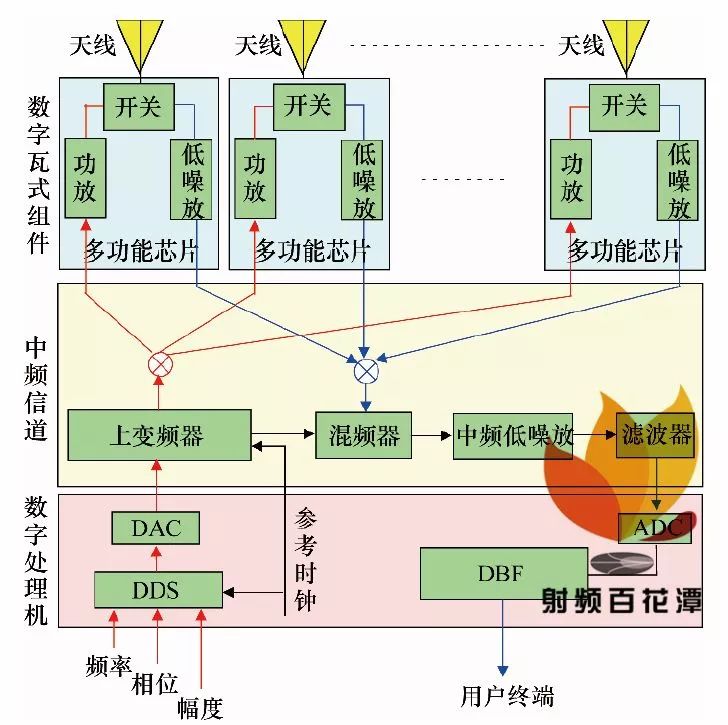

所谓有源相控阵天线,就是在每个天线单元通道中设置固态发射/接收组件[13],其典型的特征就是在每个天线单元发射通道中集成了功率放大器和在每个天线单元接收通道中集成了低噪声放大器。典型的有源相控阵天线主要包括天线阵面、TR 组件、馈电网络、波控器、电源( 含信号调制器) 、以及结构件( 含散热装置) 等,如图1 所示。

图1 典型的有源相控阵天线系统组成

天线阵面主要包括辐射单元、金属基板、射频接插件等。TR 组件包括TR 腔体、PCB 板或LTCC 板、软基片、功率放大器、低噪声放大器、移相器、串并转换、滤波器,温度补偿、射频接插件、以及低频接插件等,对有源相控阵天线来说,TR 组件占成本的主要部分。馈电网络包括收发共用馈线、发射功率分配网络,以及接收信号合成网络; 通常情况下,为了确保接收支路的增益和使发射支路的末级放大器推饱和,需要在接收支路中增加驱动级低噪声放大器和在发射支路中增加驱动级功率放大器,对于有单脉冲测角要求的,馈电网络还需设计成和波束、方位差和俯仰差波束接收通道,这些都会导致有源相控阵天线成本增加。波控器核心器件是FPGA,其主要功能是将终端控制命令计算成控制TR 组件内移相器的TTL /LVTTL 电平,并生成移相码,从而改变天线阵面信号相位因子,完成有源相控阵天线的波束快速扫描,此外波控器还可以具有电源分发的功能,从而实现给TR 组件内的芯片供电,并具备校准测试的配合执行功能( 适应TR 组件自动测试和天线内/外校准功能) 。电源主要实现的功能是将直流电压转换成各个器件需要的电源值,即DC /DC 转换,对于脉冲工作体制的天线,电源还需包含信号调制器,从而实现连续波信号转换成脉冲信号。

有源相控阵天线成本分析

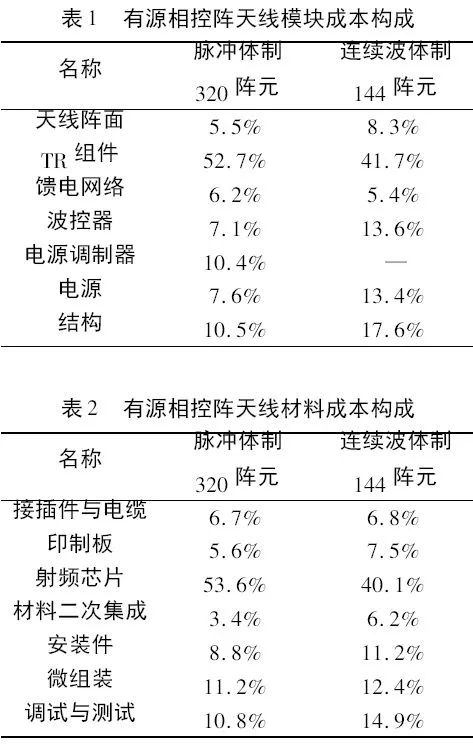

对于成本组成而言,不同体制、不同规模、不同频率、不同输出功率的有源相控阵天线的成本组成是有变化的,但统计数据可以看出其成本组成的趋势。以实际工程为例,其各个模块的成本构成如表1 所示,在有源相控阵天线的成本中,TR 组件的成本占有重要比重。表2 所示为有源相控阵天线的材料成本,可以看出射频芯片在成本中占有重要比重。因此降低有源相控阵天线的设计成本,应从简化有源相控阵天线( 主要是TR 组件) 的构架、提高芯片集成度、以及减少射频通道数出发。需要说明的是,表1 和表2 给出的成本统计分析均为瓦式有源相控阵天线,对于砖式有源相控阵天线,其成本的构成趋势是一致的。

降低有源相控阵天线研制成本包括研究、开发、生产、管理等多个方面,但在技术上降低成本的措施常常是至关重要的,本文将重点探讨有源相控阵天线低成本设计的技术路线和实施方案。

总体设计思路

要降低有源相控阵天线成本首先可以通过选择合理的系统体系构架来实现,即采用瓦式电路布局设计方法。因为瓦式技术可以大幅减少印制电路板和连接器的数量,并能通过大规模微波制造技术和封装工艺使有源相控阵天线成本降低,甚至可以做到只有砖式电路布局设计技术的1 /5[13-14]。

在上述瓦式构架设计的基础上,有源相控阵天线进一步降低成本的方法就是减少芯片的使用数量,提高芯片的多功能和多通道集成度[15]。其核心思想是在一块芯片里集成功率放大器、低噪声放大器、射频开关、移相器,以及数字控制电路等,从而达到减少有源相控阵天线的芯片数目、互连工序与连线,以及减少芯片电路面积和简化芯片外围电路的目的,同时通过采用硅基异构集成工艺,将多个通道集成在一块晶圆级芯片上,提高了TR 组件的集成度和综合性能,大幅降低有源相控阵天线的成本。同时,将数字技术与相控阵天线技术相结合,在发射与接收模式下以数字波束形成( DBF) 技术取代传统移相器、衰减器、波束形成网络、和波束控制器,便产生了数字阵列相控阵天线[16-17]。对于数千阵元的大规模有源相控阵天线,当取消掉数千个移相器和衰减器、一套波束形成网络和一套波束控制器时,其波束扫描完全依赖于后端的数字处理机和软件来实现,可以降低上百万的成本。

瓦式架构、多功能芯片集成以及数字阵列技术均是从减少元器件数量和工艺互连的角度进行的低成本设计思路。从技术上分析,降低有源相控阵天线成本的思路还可以在保证阵列增益不降( 或提高) 的前提下,进一步减小阵列规模/数量( 射频通道数) 。一种有效的技术途径就是采用宽带宽角扫描技术来实现。这种方法避免了采用稀疏阵在降低相控阵天线成本的同时阵列增益也下降的缺陷。此外,在有源相控阵天线工作体制能够兼容的情况下,还可以将多副窄带相控阵天线用一副宽带相控阵天线来实现[18],通过采用数字多波束形成技术,以实现多个目标、多个任务的兼容,最终实现相控阵天线成本的最优化。

具体实施方案

针对上述总体设计思路,图2 给出了典型的数字阵列相控阵天线的设计框图,它由阵列天线、数字TR 组件( 多功能芯片组件) 、中频信道、数字处理机组成。直接数字综合器( DDS) 输入信号主要包括频率、相位、幅度3 个二进制形式的控制信号,以及一个时钟信号( 参考频率) 。发射时,由DDS 产生的基带信号经数模转换器( DAC) 变成模拟信号,经上变频器后产生相控阵天线的发射激励信号,再经数字TR 组件的功率放大器传送到天线单元,最后由各天线单元的辐射信号在空间合成所需的发射方向图。接收时,DDS 产生本振基带信号,经DAC 和上变频器后变为接收本振信号,与数字TR 组件的低噪声放大器接收下来的天线单元的射频信号进行混频,获得中频信号,再经中频放大器、滤波器、模数转换器( ADC) 变换,获得二进制形式的数字信号,最后通过DBF 实现自适应波束形成和软件化信号处理,传到用户终端。

图2 数字阵列相控阵天线设计框图

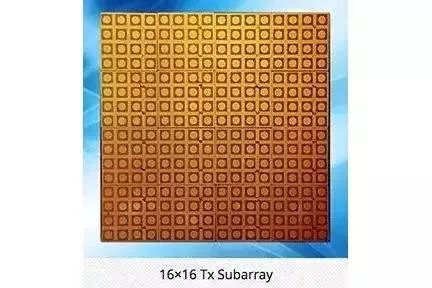

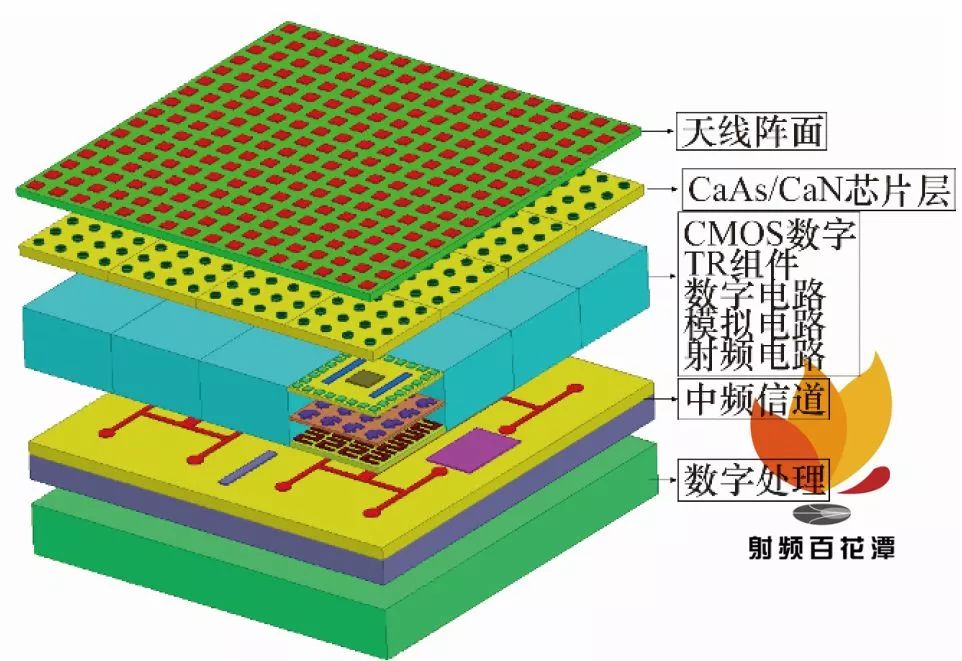

数字阵列相控阵天线除了从设计体制上可以大幅降低成本,还可以采用瓦式架构设计技术和多功能多通道集成方法( 或一片式集成思路) ,通过硅基工艺( CMOS) 将设计成本降得更低[19]。虽然CMOS工艺可以在同一芯片上集成模拟电路、数字电路和射频电路等功能模块,但CMOS 工艺的缺点是发射通道输出功率低( 毫瓦量级) 、接收通道噪声大( 通常大于4 dB) ,当有源相控阵天线发射功率较大或接收能力较强时,有效的解决办法是采用砷化镓或氮化镓放大芯片作为末级放大,以提高有源相控阵天线的发射功率或接收能力。在结构简化设计方面,综合利用片上系统( SOC) 和系统级封装( SOP)技术的优势,将不同学科、不同材料、不同功能的电路通过多层异质基板和3D 堆叠集成到同一个封装内,完成高/低频混合集成,最终实现低成本数字瓦式有源相控阵天线,如图3 所示。SOP 和SOC 技术的综合应用,体现了一体化设计、一体化制造、和3D叠装的思想,使电子产品具有当前最佳的小型化、低成本、高性能、高可靠性的异质异构集成方式。这种集成方式去掉了传统二次集成的多重封装、接口、连接电缆和结构装配,减少了材料消耗,降低了成本。同时,根据远场叠加原理,阵列在扫描角域的增益跟单元波束宽度和阵列规模有关,如果能有效提高在大扫描角域的单元方向图增益,就能减少阵列规模,从而减少有源相控阵天线的设计规模。

图3 低成本瓦式数字相控阵天线设计方案

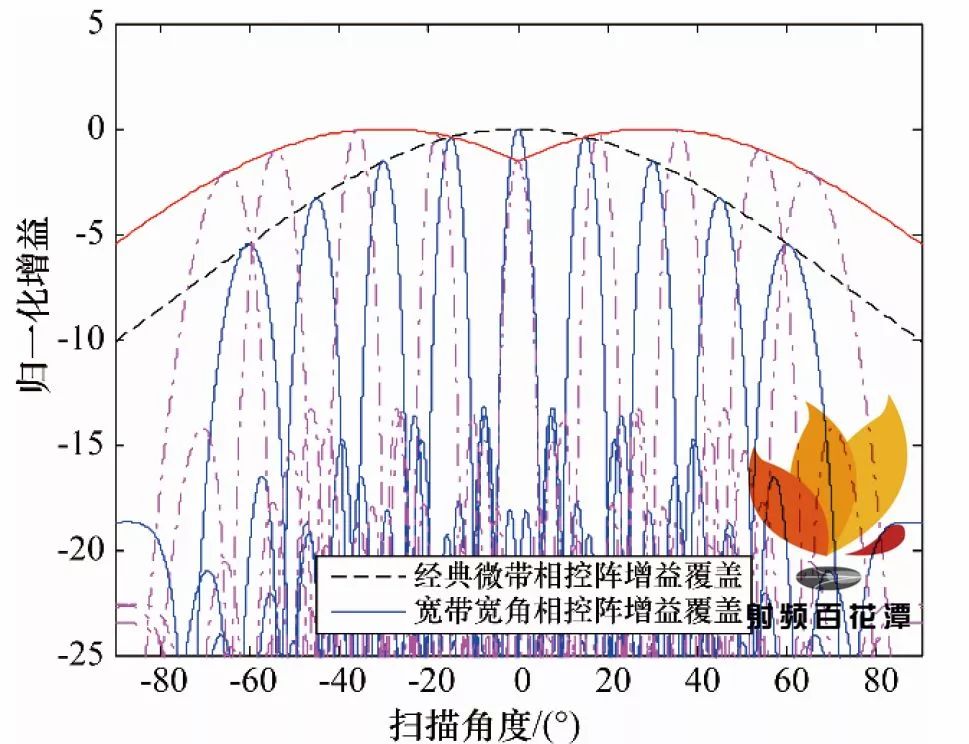

采用单元方向图可重构技术[20],可以有效提高大扫描角域的单元方向图增益,实现该目标。因此,将宽带多波束天线设计技术和可重构宽角扫描阵列技术结合起来,能够显著降低有源相控阵天线的设计规模、收发通道,以及元器件的使用数量,使有源相控阵天线的成本降到最低。大量的工程实践表明,经典的微带相控阵天线在大扫描角±60°时增益会下降5 dB左右,采用方向图可重构天线作为有源相控阵天线的辐射单元,可以在±60° 角域天线阵列增益提升3 dB左右( 如图4) ,这样就可以确保在扫描角域内阵列增益不变的情况下,阵列规模可以减少一半。

图4 可重构宽带宽角扫描数字相控阵天线方向图

在低成本有源相控阵天线的设计中,首先应在概念上有所创新,探索新原理和新方法。本文提出将数字技术、多功能芯片集成与瓦式相控阵天线技术相结合,从系统总体方案中简化系统架构和互连工艺,并去掉昂贵的移相器芯片,用数字波束形成( DBF) 方法来降低有源相控阵天线的成本,最后从缩减阵列规模和射频通道的角度从发,提出宽带宽角扫描的数字有源相控阵天线设计技术来实现低成本。通过这些总体思路和设计方法,能够使有源相控阵天线的设计成本达到最优化,满足用户的使用

需求,从而解决数十年来有源相控阵天线因造价昂贵很难在某些领域应用的难题。本文是第一篇详细报道有源相控阵天线低成本总体设计技术的论文,它能大幅提升我国有源相控阵天线的自主创新能力,为后续建立起完善的、可持续发展的先进相控阵天线的研发、制造、应用奠定基础。

往期热文(点击文章标题即可直接阅读):