训练时间降低90%以上!世界最大的芯片WSE有望打破AI计算瓶颈

新智元报道

新智元报道

来源:IEEE

编辑:大明、edein

【新智元导读】还记得几个月前问世的世界最大的AI芯片吗?IEEE Spectrum团队最近访问了其制造商Cerebras的工厂,并对CEO和技术团队进行了访谈,Cerebras CEO表示,这款划时代的芯片有望突破AI的计算瓶颈,将训练时间由几周缩短到几小时。戳右边链接上 新智元小程序 了解更多!

人工智能计算机初创公司Cerebras Systems CEO兼联合创始人Andrew Feldman表示,如今的人工智能仅仅只是开始。

正如他及其同僚所言,问题在于当今的深度神经网络十分耗时且计算密集,训练非常困难。比如,自动驾驶汽车要识别道路上遇到的所有重要物体,神经网络需要向其显示所有物体的很多、很多相关图像。这一过程在数据中心进行,由耗电数十有时甚至数百千瓦的计算机完成,任务时间经常长达数周。

Cerebras的客户抱怨说,使用当下的计算机训练大型神经网络的时间可能长达6周。照这样,一年只能训练6个神经网络。“只有验证更多想法才会产生新想法,” Feldman说。“如果能在2或3个小时内完成[网络训练],就可以尝试数千个想法。”

当IEEE Spectrum访问位于美国加州Los Altos的Cerebras总部时,这些客户及一些潜在客户已经通过橙色光缆把他们的训练数据输入4台CS-1计算机。这些64厘米高的机器运转起来,每台消耗20千瓦,散发的热量通过墙上的一个洞流到硅谷的大街上。

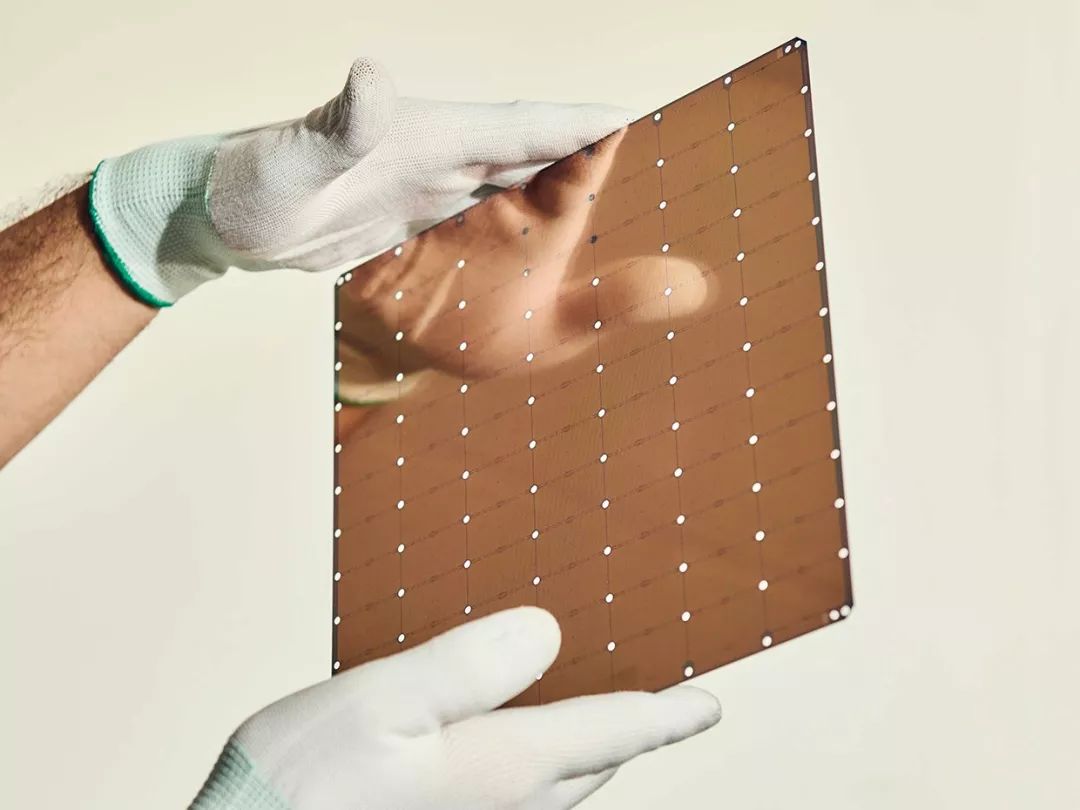

从外面看,CS-1机身并不大,每个机箱大约3/4是冷却系统,余下的1/4则是真正的革命:一台性能强悍的计算机,几乎完全由一整块芯片组成。这块芯片的面积高达46,255平方毫米,是任何一块可以买到的处理器芯片的50+倍。这就是由Cerebras生产的世界最大芯片Wafer Scale Engine (WSE),它有12,000亿个晶体管,400,000个AI可编程内核,18 GB超快速片上存储器(SRAM)和100Petabits /s的结构带宽。

Cerebras的统计数据令人震惊。据称,一个10机架TPU二代集群(现在已更新为Google AI计算机的第三代集群)所耗电量是其5倍,占用空间是其30倍,而性能仅有搭载WSE芯片的计算机的1/3。单块巨型芯片是否真正是AI社区所需,相信这个答案从今年开始就会清晰起来。美国加州山景城公司LinleyGroup的高级分析师Mike Demler说:“ [神经网络]模型日益复杂,能够快速训练或再训练确实很重要。”

Feldman说,2015年当Cerebras的创始人们开会时,他们想要打造完全适配当下AI工作场景的计算机,这些工作场景有若干项定义:它们需要快速移动大量数据,它们需要内存接近于处理器内核,并且这些内核不需要处理其他内核正在处理的数据。

这立即给了公司资深的计算机架构师一些启发。首先,他们可以使用成千上万个专门用于神经网络相关计算的小型内核,而不是更少、更通用的内核;其次,这些内核应该互连在一起,可以快速而低耗的移动数据;最后,所有数据应该在处理器芯片上,而不是在单独的存储芯片上。

在这些内核之间来回移动数据的需求,正是WSE独特性的来源。两个内核之间移动数据最快、能耗最低的方法是将其放在同一硅基片。当数据必须从一个芯片传输至另一个芯片时,由于距离更长并且传递信号的“电线”必须更宽并且包装密度更低,从而在速度和功耗上大打折扣。

所有通信在硅上的驱动力,以及对小内核和本地存储器的渴望,都表明要尽可能生产大芯片,也许是整个硅晶圆那么大。Feldman说,很明显,我们做不到这一点,但是这显然有很大的好处。

数十年,工程师一直认为晶圆级芯片是一条死路。毕竟,IBM System/360大型机的首席架构师Gene Amdahl曾在一家名为Trilogy Systems的公司尝试并失败了,但它足够令人称奇。但是Lauterbach和Feldman说,任何与Amdahl方法的对比都已经过时。当时Amdahl使用的晶圆尺寸只有现在的1/10,而晶圆上相关器件的尺寸则是现在的30倍。

更重要的是,Trilogy无法处理生产芯片时出现的不可避免的错误。如果其他所有条件相同,随着芯片增大,缺陷的可能性也会增加。如果你的芯片尺寸接近于一张信纸(8.5" *11"规格),那么缺陷在所难免。

但是Lauterbach看到了一种架构解决方案:由于他们针对的工作负载倾向于拥有数千个相同的小型内核,因此可以嵌入足够多的冗余内核,这甚至可以解决1/100的缺陷造成的故障,并且依然不失为一块功能强劲的大型芯片。

当然,Cerebras仍然不得不解决许多制造问题,才能打造其容错性的giganto芯片。比如,光刻工具被设计为将其定义特征的样式投射到相对较小的矩形上,并一遍遍重复进行。由于在晶片不同位置浇铸不同样式的高昂成本和巨大困难,这样已经把打造单一晶圆的许多系统拒之门外。

Cerebras内部:冷却系统占CS-1大部分,WSE芯片位于左后角。

但是WSE无需这样。它就像布满相同芯片的典型晶圆,与你平常制造的一样。最大的挑战是把这些伪芯片连接在一起。

芯片制造商在每个芯片周围留下空白硅的细长边缘,称之为划片线。晶圆通常沿着这些线切成小块。Cerebras与台积电(TSMC)合作开发了一种跨划片线建立互连的方法,使每个伪芯片中的内核皆可通信。

现在,所有通信和内存在一块硅片上,数据传输可以畅通无阻,从而产生每秒1,000 PB的内核到内核带宽和每秒9 PB的SRAM到内核带宽。Feldman说,这不仅仅是多,而是带宽4个数量级的提升,因为我们在硅片上。

跨划片线互连并不是需要的唯一发明。制造芯片的硬件必须进行改良。即使电子设计自动化软件也要进行定制才能在如此大的芯片上工作。Feldman说,每条规则,每个工具,每个制造设备都旨在拾取一块正常大小“巧克力芯片曲奇”,而[我们]要交付的是整个曲奇烤盘;方法的每一步,我们都必须发明。

他接着说,晶圆级集成在人们视野中消失了40年,但它肯定会在某个时候再出现;既然Cerebras已经做到,那扇门可能也会向其他人打开。“我们认为其他人将寻求与我们合作解决AI以外的问题。”他又说。

2018年,Google、百度及一些学术顶级机构开始制定基准,允许系统之间进行一一对应的比较。结果,MLPerf于2018年5月发布了训练基准。

借助这些基准,神经网络训练技术在过去几年取得长足进步。Nvidia DGX SuperPOD(本质上是有1,500块GPU的超级计算机)可在80秒内完成ResNet-50图像分类问题,与之相比,Nvidia DGX-1(大约在2017年)花费了8个小时,K80(在2015年)花费了25天。

Cerebras尚未发布MLPerf结果,以及任何其他可独立一一核对的结果。相反,他们更倾向于让客户使用自己的神经网络和数据来试用CS-1。

分析师认为,这种做法很常见。“每个公司都根据自身业务开发相关模型,” Moor Insights的AI分析师Karl Freund说。“这是客户唯一关心的事情。”

举个例子,早期的客户阿贡国家实验室的需求很大。最近在训练神经网络以实时识别不同类型的引力波事件时,科学家使用了阿贡实验室耗电兆瓦级别的Theta超级计算机(排名第28的全球最强大系统)资源的1/4。

把功耗降到仅几千瓦对超算来说似乎是一个核心优势。这是否是一个吸引数据中心的卖点,不幸的是Lauterbach对此表示怀疑。他说:“虽然许多数据中心都在谈节能降耗,但只是口头说说,实际上并不在意,他们真正想要的是性能。这当然是一个几乎和餐盘差不多大小的处理器芯片所能满足的。”

原文链接:

https://spectrum.ieee.org/semiconductors/processors/cerebrass-giant-chip-will-smash-deep-learnings-speed-barrier

图文直播|新智元小程序技术公开课第一期!

1月6日晚,16本Phthon系列教材作者董付国将在新智元小程序揭秘「如何编写有“Python味道”的Python代码?」,当天还有机会与大咖在线互动,答疑解惑,现在扫描下方海报二维码可抢占免费预约名额。