为什么我们需要开源的系统芯片?

作者 | bunnie

译者 | 弯月,责编 | 杨碧玉

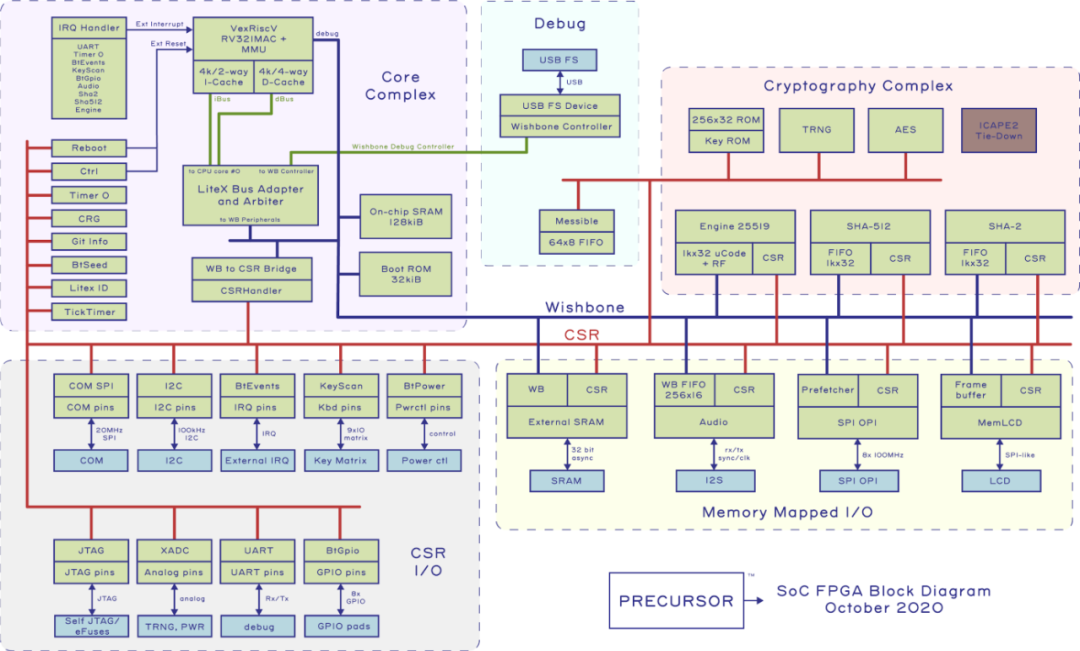

现代的小型电子产品往往基于某个高度集成的芯片构建,这种芯片称为“系统芯片”(System on aChip,缩写:SoC)。最早的家用计算机主板大约包含一百多个芯片,然而当80286 PC/AT兼容机成为主流后,在摩尔定律的推动下,主板上的芯片减少到了寥寥几个,而且这个行业永远不会走回头路。现在,典型的SoC可以集成一个CPU核心组件,以及数十个外围设备,包括模拟、RF和电源等功能。我们甚至还有“系统级封装”解决方案,可将SoC、RAM,有时甚至将FLASH芯片封装到一个塑封中。

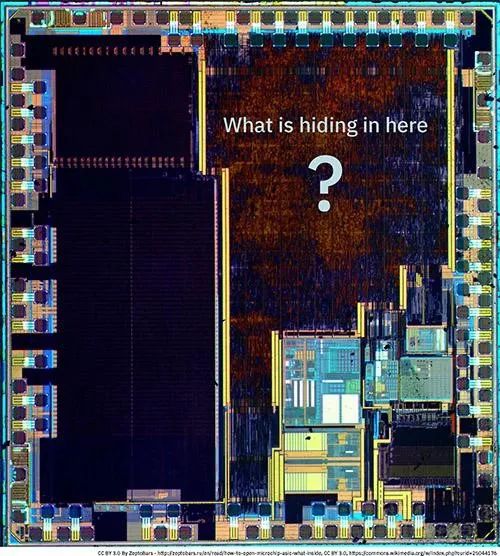

现代SoC极其复杂。现代SoC完整的“用户手册”往往长达几千页,而bug列表也有几百页。我在“用户手册”上加了引号,因为即使是最开放、文档最齐全的SoC(例如NXP的i.MX系列),也必须签署严格的保密协议,才能阅读各种第三方知识产权功能模块对应的数千页文档,例如视频解码、图形加速以及安全等。除了需要保密协议的文档之外,通常还有数千页未发布的、针对那些不再使用的芯片区域的文档,例如原本设计中包含但最终未能成功的外围设备,内部调试工具以及预引导工具等。许多不再使用的功能,甚至连设计芯片的团队都不知道!

不再使用的芯片区域是一件大事,因为构建芯片可不像搭乐高积木那般简单,它更像是雕刻家刻在大理石快上的雕塑,因此添加电路的难度远远高于关闭电路。增加一条电路仅制作新的掩膜就大约需要花费100万美元,同时还会导致项目延迟70天(大约10万人时的额外工作)。而在正确计划的情况下,关闭一条电路非常简单,只需要修改代码,或者针对某个掩模层进行轻微改动,只需要花费大约1万美元以及几天的延迟(假设晶圆尚处于中期阶段,很容易进行这样的改动)。

LiteX:Precursor系统芯片背后的框架

Precursor系统芯片简介

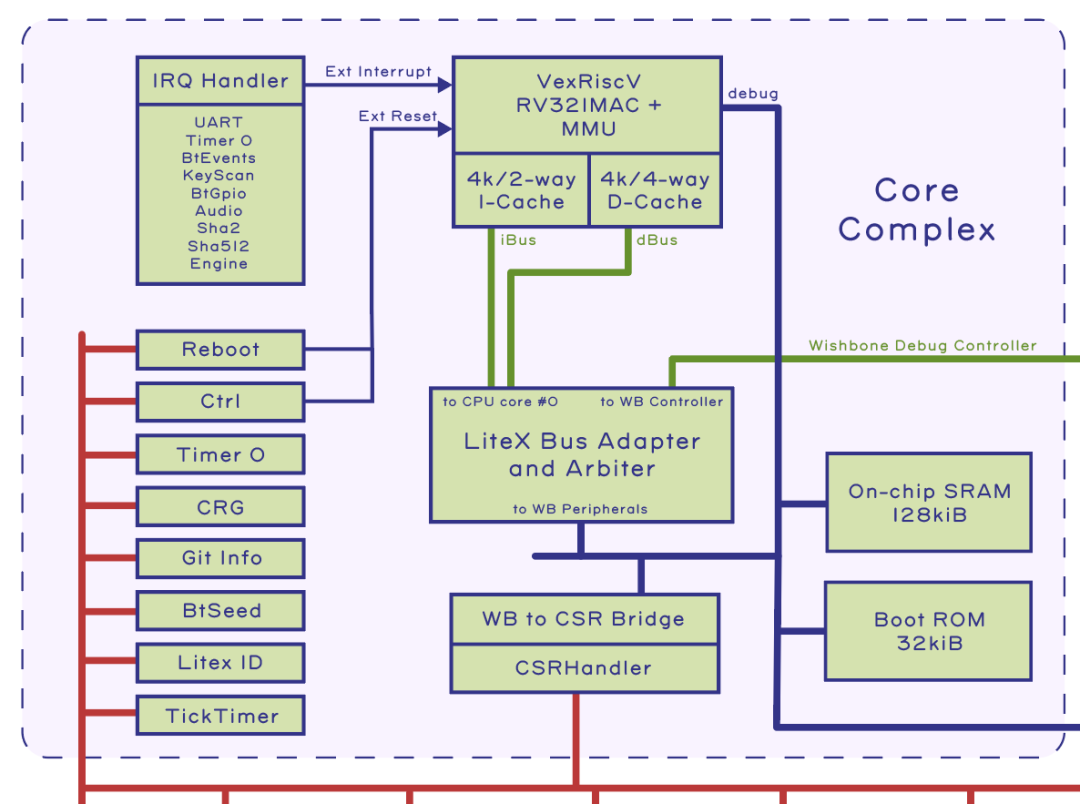

核心区域

“Reboot”可以为重置向量指定一个新位置

“Ctrl”可以发送软重置

“Timer 0”是LiteX提供的默认定时器。这是一个高解析度的32位定时器,时钟频率与CPU核心频率相同。

“CRG”是负责控制FPGA时钟生成器的接口。目前我们还没有考虑太多,但最终它将在电源管理和延长电池寿命方面发挥重要作用。

“Git Info”是一个静态寄存器,提供用于构建Precursor芯片的git代码库的信息。

“BtSeed”是一个64位数,经过随机初始化后可以为布局布线过程提供一个熵。如果最终用户要求为其设备设计独有的FPGA网表,那么通过BtSeed,无需改动代码就可以实现(否则所有构建都是完全相同的)。

“Litex ID”是一个可供人阅读的文本字符串,用于标识系统芯片设计。

“TickTimer”是一个低分辨率的64位定时器,时钟增量为1毫秒。它作为Xous OS的时钟源使用。

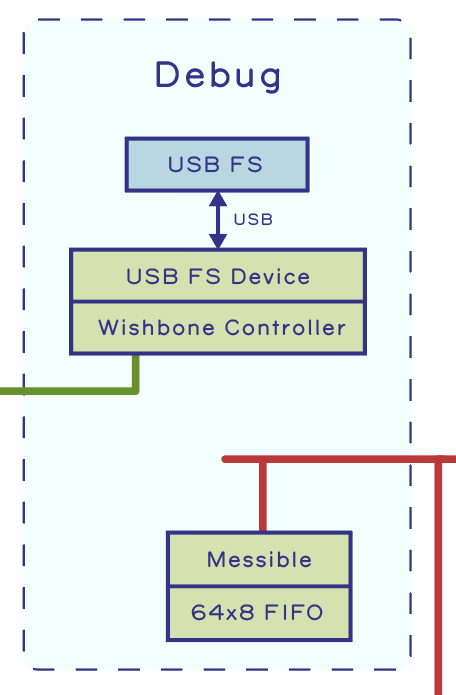

调试块

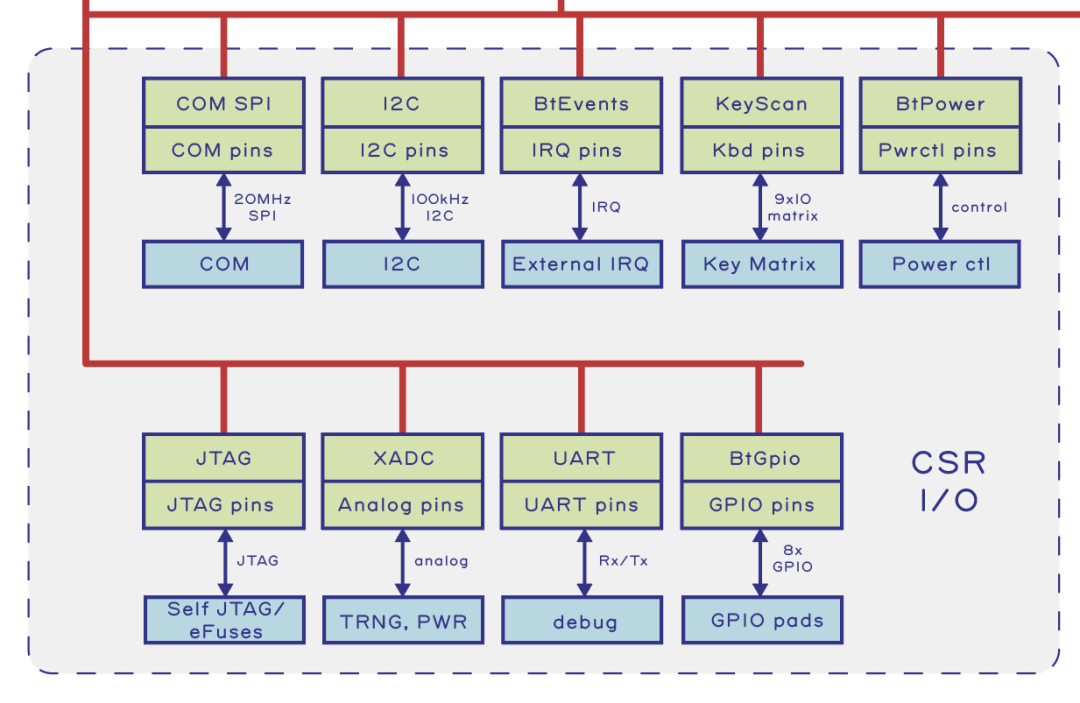

内存映射和CSR I/O

“COM SPI”是连接到嵌入控制器(EmbeddedController,EC)系统芯片上 的SPI总线。这是一个20MHz的SPI外设,传输带宽为固定的16位。该块的目标为升级成内存映射I/O块。

“I2C”是一个I2C总线控制器。目前,只有实时时钟(RTC)芯片和一个音频编码解码芯片连接到了这个I2C总线上。

“BtEvents”是一个负责各种外部实时终端的catch-all类型的块。目前它负责处理来自EC和RTC芯片的中断。

“KeyScan”是键盘控制器。它负责扫描9x10的键盘矩阵来发现击键,使用一个慢速的32kHz外部时钟源。将键盘扫描器与系统核心时钟解耦合,系统就可以在等待键盘输入时进入更低功耗状态,从而将Precursor在两次充电之间的使用时间延长数天。

“BtPower”是一组GPIO,专用于电源管理。它可以将音频和离散的TRNG打开或关闭,覆盖EC的电源控制指令,为USB type C端口激活boost模式(以支持DFP“宿主”操作),还可以采用自毁机制。

“JTAG”是一组GPIO,连接到FPGA的JTAG引脚。这些与我们的eFuseAPI驱动结合使用,可以在7 Series FPGA上自行提供AES比特流加密。

“XADC”是7 SeriesXADC块的接口。它是一个12位的多通道ADC。主要用于自我监测系统电压。在最终的产品版本中,至少有一个通道的ADC可以用于GPIO内部头的配置项,这样用户可以很容易地将模拟传感器集成到Precursor中。

“UART”是一个简单的115200、8合一串口,连接到控制台I/O的调试头。

-

“BtGpio”是一个数字I/O块,用于在GPIO内部头上驱动引脚。注意由于FPGA的实现限制,在不更新比特流的情况下无法在数字GPIO和模拟GPIO功能之间切换。

-

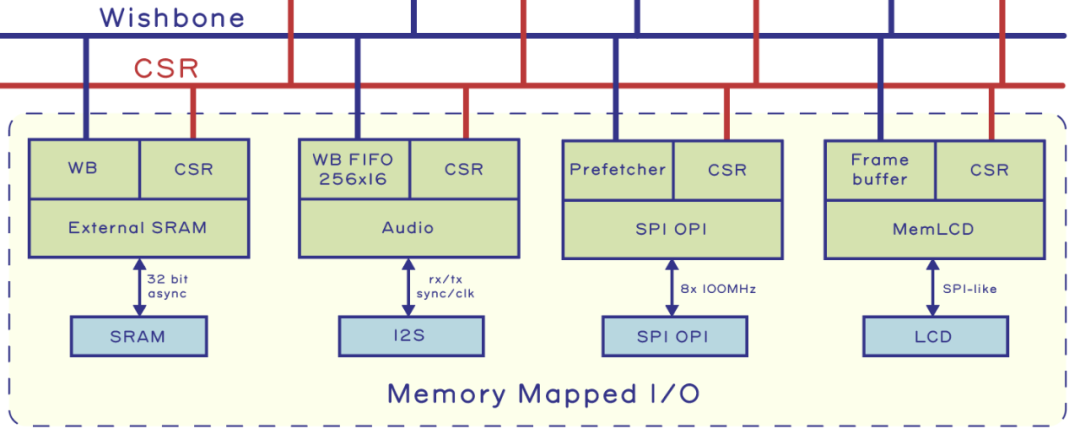

“External SRAM”是一个32位宽的一部接口,映射了16MB的外部SRAM。这些SRAM由电池供电,所以在系统芯片断电时也可以保持状态。这样做的目的是通过减少睡眠和唤醒的额外开销来优化电力消耗。但是,这也意味着自毁过程必须先清除SRAM中的敏感数据,才能启动清除系统芯片的过程,因为自毁电路也是由SRAM的备用电源负责供电的。外部SRAM块还有一个CSR接口,负责从SRAM中读取配置模式。 -

“Audio”是一个连接到外部音频编码解码的I2S接口。它包含一个用于配置I2S接口的CSR块,还包含一对256x16的、映射到内存的采样FIFO。 -

“SPI OPI”是一个类似于SPI的高速接口,连接到外部闪存存储,并映射了12个8MB的非易失性存储器上。OPI中的“O”代表八位,这是一个8位总线,频率为DDR的100MHz。它还包含一个与读取器,可以存储相当于数个缓存线的代码,可以优化顺序代码执行的情况。该总线的高性能非常重要,因为它主要被CPU用来运行代码。它还包含一个CSR接口,用于控制诸如块擦除、页面编程等操作。 “MemLCD”是LCD的帧缓冲。Sharp Memory LCD包含自己的内部内存,因此即使宿主断电,也能够维持图像。因此,MemLCD帧缓冲就是LCD自身的缓冲。它负责管理LCD中的哪些线需要重画,在CSR上有请求发生时,它只会刷新那些需要重画的线。这样可以提高LCD的感知刷新率。如果重画整个屏幕,那么刷新率只有10Hz;但屏幕上的静态内容越多,刷新率也就越高。

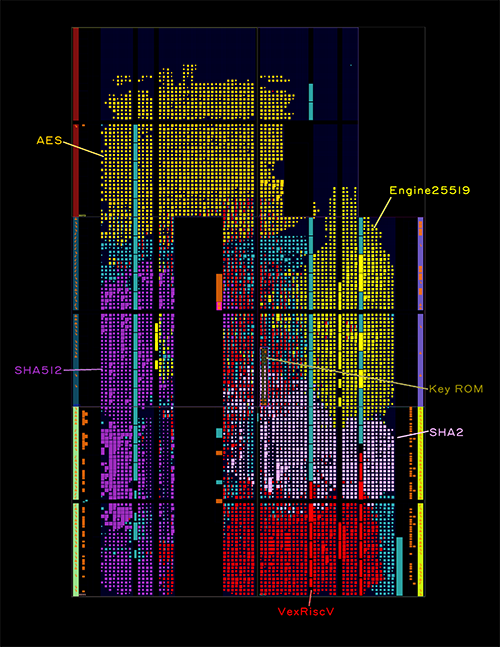

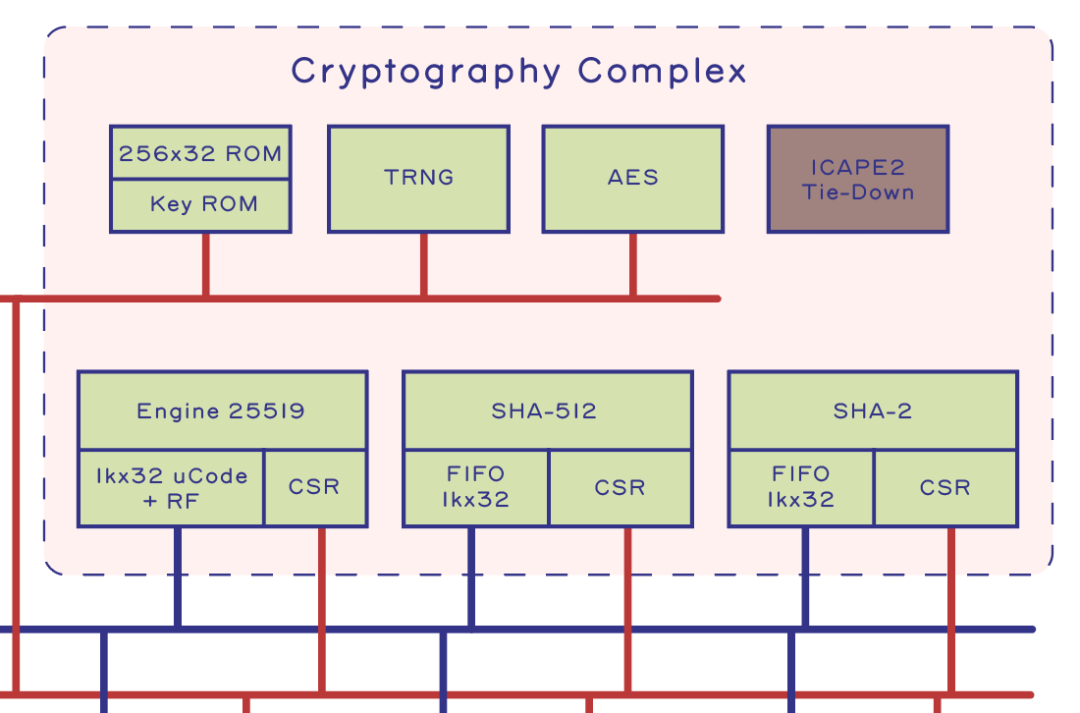

加密区域

“Engine25519”是算术加速器,用于加速2^255-19质数域中的操作。它是一个微指令的256位算术引擎,计算带有正规化的256位乘法仅需要大约1微秒,比在RISC-V CPU上运行同等操作大约快30倍。它需要消耗大量的资源,但依然非常重要,因为Betrusted安全通信应用程序建立在Double-Ratchet算法上,该算法非常依赖这种运算。要理解Engine25519,最好从CI文档开始阅读。该块非常大,稍后我们会单独写一篇文章来解释它的功能。

“SHA-512”和“SHA-2”是硬件加速的SHA散列块。它们来自Google的OpenTitanSystemVerilog源代码。SHA-2块直接来自OpenTitan,几乎包括了OpenTitan的所有代码,因为它非常容易集成。SHA-512块是我们自己对SHA-2块的改进。由于历史原因,目前的Precursor中同时包含了两个快,尽管绝大部分应用程序仅需要其中一种。

“AES”是一个AES加速器,也直接来自Google的OpenTitan项目。它可以支持AES 128、192和256,还支持ECB、CBC和CTR模式下的加密和解密。

“KeyROM”是一个256x32的ROM,使用FPGA中的固定位置LUT实现。由于ROM的位置是固定的,我们可以使用PrjXray来确定FPGA比特流中KeyROM比特的位置。这样就可以在FPGA比特流中直接编辑KeyROM,从而将信任从低层的eFuse AES key传递到Precursor系统芯片中的高层功能中。我们会在其他文章中进一步讨论一些最近发现的FGPA eFuse AES key的重要脆弱性。

“TRNG”是芯片内的、基于环形振荡器的真随机数生成器。它使用多个小环来收集足够多的熵,然后合并成一个大环,用于最终的测量。Precursor TRNG的构建和验证也会另文介绍。

“ICAPE2”是在FPGA构造(fabric)中对未使用的内部调试端口的显式绑定(tie-down)。ICAPE2是Xilinx采用的方法,FPGA可以通过它进行内省,并访问内部配置状态。我们显式地将其绑定,这样其他功能就无法使用它。此外,由于ICAP2位于比特流中众所周知的位置,实际上可以写一个工具,在编译后对比特流进行检查,以验证ICAP2块确实被禁用了。

分块的思路

原文:https://www.bunniestudios.com/blog/?p=5971

本文为 CSDN 翻译,转载请注明来源出处。

更多精彩推荐

☞中国开源燃烧!Zilliz 获全球开源基础软件最大单笔融资 4300 万美元

![]()

点分享

![]()

点点赞

![]()

点在看