本文介绍先进雷达波形发生器(ARWG)。ARWG 是软件定义电子战系统系列的一部分。它是在商用 AMD-Xilinx Gen3 射频片上系统中以 ZCU208 评估板的形式实现的。它提供了一个灵活的平台,用于生成用户定义的雷达脉冲,具有脉冲内调制、近乎实时的自定义波形生成、脉冲到脉冲频率灵活性、用户定义的幅度、频率和相位调制以及复合脉冲群生成等复杂功能。它包括多个用户界面,包括串行命令行界面和基于 Python 的图形用户界面。ARWG 通过千兆以太网接口与支持的个人电脑 (PC) 相连,因此可以与驻留在 PC 中或跨网络的强大应用程序进行交互。本文讨论了 ARWG 的基本设计和主要功能,并展示了示例功能。

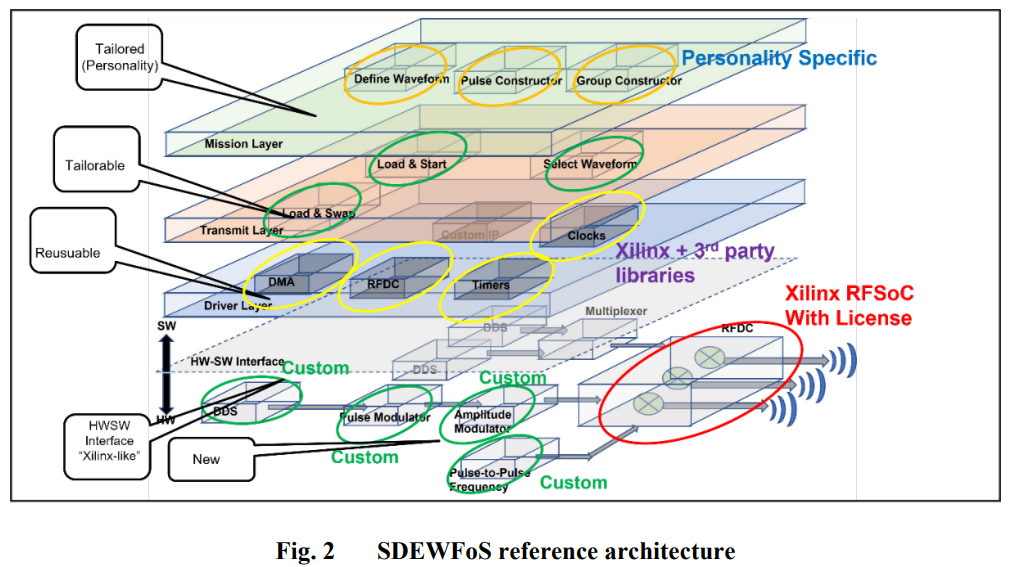

图 软件定义电子战系统(SDEWFoS)参考架构

ARWG 是在 ZCU208 评估板外形尺寸的 Xilinx Gen3 RFSoC 上以裸机配置实现的。这包括 Zynq PS 中的高级精简指令集计算机机 (ARM) Cortex A53 四核微处理器,以及可编程逻辑 (PL) 分区中的 XCZU48DR-2FSVG1517 Ultrascale+ 现场可编程门阵列 (FPGA)。这有助于实现强大的 SW-HW 代码设计,在 PS 中使用灵活的 C 编程语言实现以控制为中心的容延流程,在 PL 中实现以数据为中心的低延迟组件。采用行业标准接口,包括高级可扩展接口(AXI)4 和赛灵思 SW 驱动程序。定制 SW 采用标准 C 语言编写,包括应用程序和硬件抽象层 (HAL) 驱动程序,并尽可能遵循赛灵思嵌入式驱动程序的惯例。本设计的 PL 中使用的所有 IP 模块都是定制设计的,采用高速集成电路硬件描述语言 (HDL/VHDL) 编写,并使用寄存器传输层 (RTL) 设计方法;不过,未来的扩展可以轻松采用任何方法生成的 IP,例如 Vitis HLS 或 MathWorks HDL Coder。

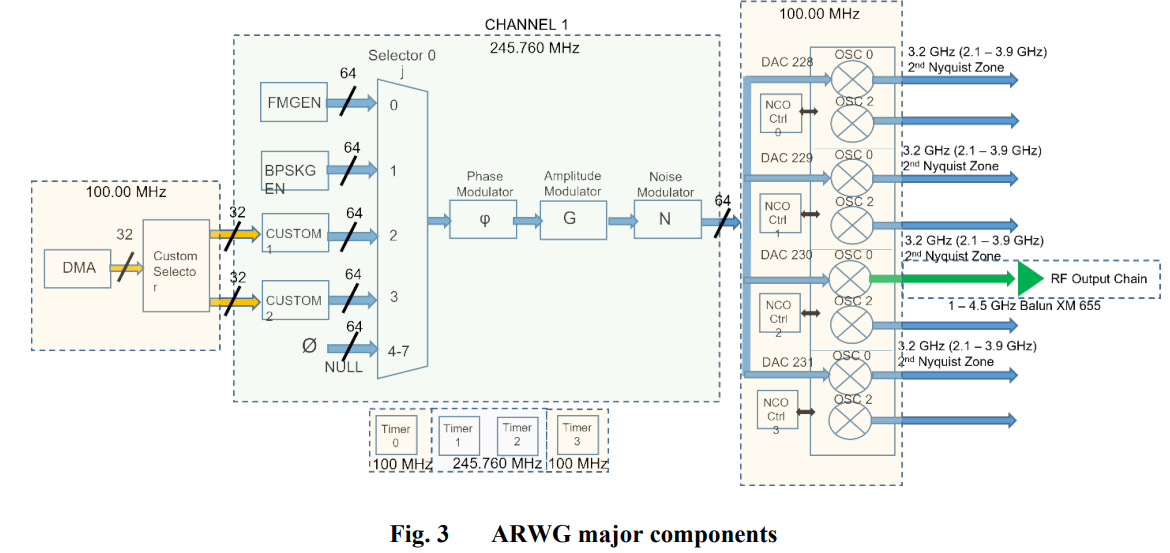

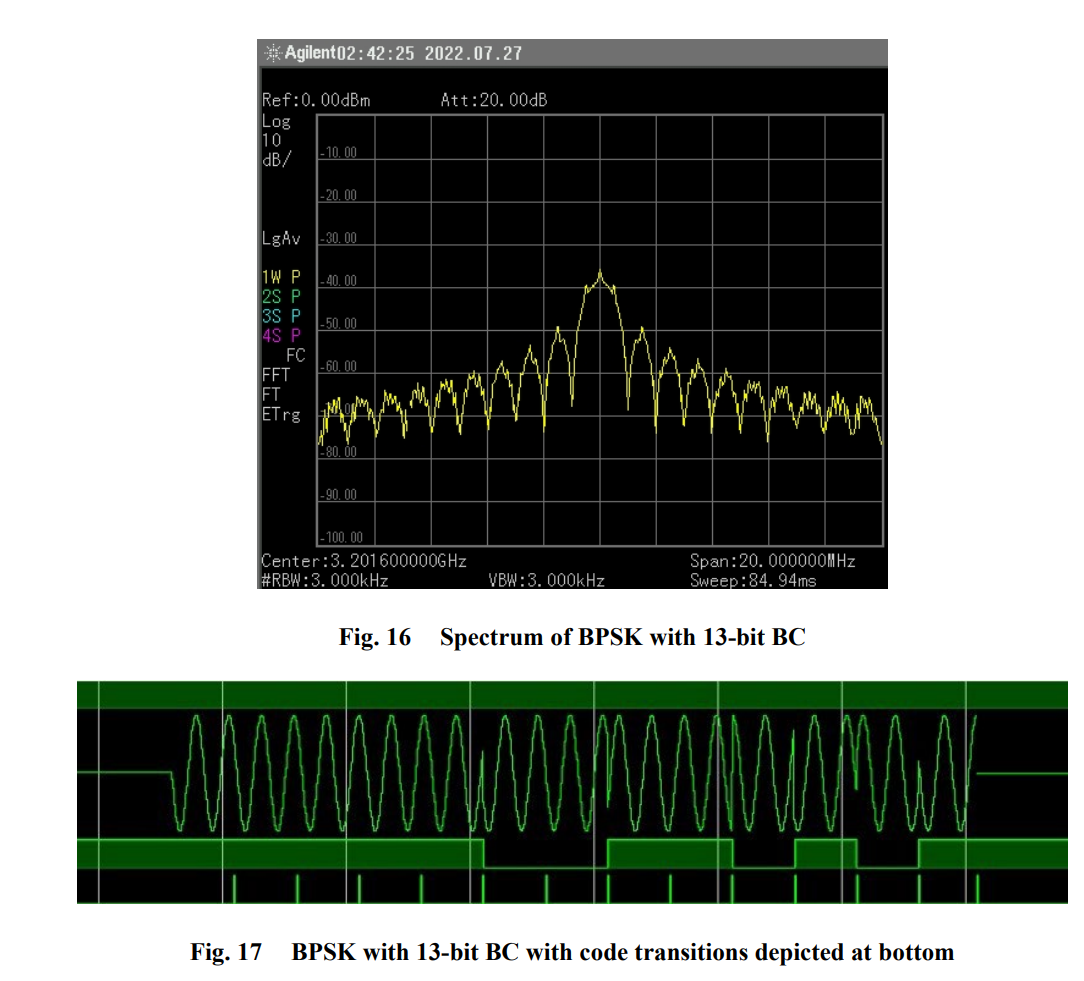

主要设计组件如图 3 所示。关键的信号发生组件是 “通道”,由四个发生器(频率调制发生器 [FMGEN]、二进制相移键控发生器 [BPSKGEN]、自定义 1 和自定义 2)、信号选择器和信号调制器(相位、振幅和噪声)组成。最终确定的 ARWG 设计将包括四个通道;本中间设计只有一个通道。存储器访问组件包括散点采集直接存储器访问(SG-DMA)外设和定制信号发生器选择器。RFDC 是 Xilinx Gen3 IP,可将数字信号转换为射频信号。四个定制数控振荡器 (NCO) 控制器 IP 实例可在每个数模 (DAC) 磁瓦上独立动态调整 RFDC 振荡器载波频率 (CF)。NCO 控制器具有低延迟特性,可在接到 SW 命令后不到 2 µs 的时间内调整 CF。最后,本设计还包括四个 Xilinx AXI 定时器;这些定时器可执行时间敏感型功能,如复杂脉冲生成和诊断功能。实际射频输出由 XM655 子卡5 提供,该子卡为下游射频消耗提供 SMA 平衡-非平衡(平衡)射频连接。完整的 ARWG Vivado IP 集成块设计见附录 A。

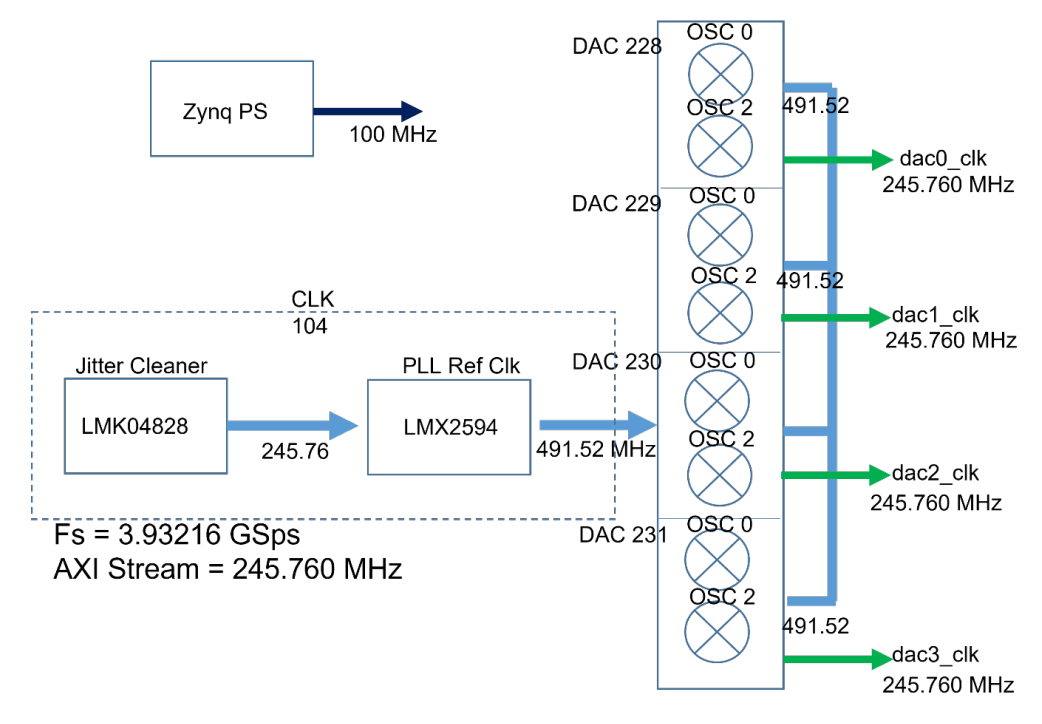

图 4 ARWG 时钟配置,包括 ZCU208 CLK104 外设、RFDC 采样时钟和 AXI 流时钟