新的 MRAM 突破有望革 CPU 设计界的命 !

过去,报道主流存储器市场的变化让人有点失望;按笼统的定义,存储器市场是指面向CPU缓存的SRAM、面向易失性RAM的DRAM以及面向非易失性存储的固态硬盘(SSD)和传统硬盘(HDD)。一方面,观看各种小众方法如何发展、它们与“典型”方法相比具有的优缺点颇有意思。另一方面,这些替代性的小众技术通常面向小众市场是有原因的。原因因技术而异,但通常一两个缺点让它们无法取代更主流的方法。真正颠覆竞争格局的突破却实为罕见;但如果Spin Transfer Technologies(STT)说的是大实话,它给市场带来的正是这种突破。

综观历史,磁阻RAM(MRAM)提供了出色的性能、数据保存和耐用性,只是很难同时集三者于一体。在最高速度下,MRAM的性能几乎与SRAM相当,但是维持这种速度所需的写入电流会降低存储器本身的性能,导致寿命短得令人无法接受。更高的写入电流与更好的数据保存成正比,但是也导致高功耗。这是阻碍该标准得到采用的一大因素――过去很难找到主流的计算场景:说到CPU缓存,MRAM是可以接受的SRAM替代方案,虽然MRAM拥有其他理论上的密度和功耗优势让它原本很适合这些市场。

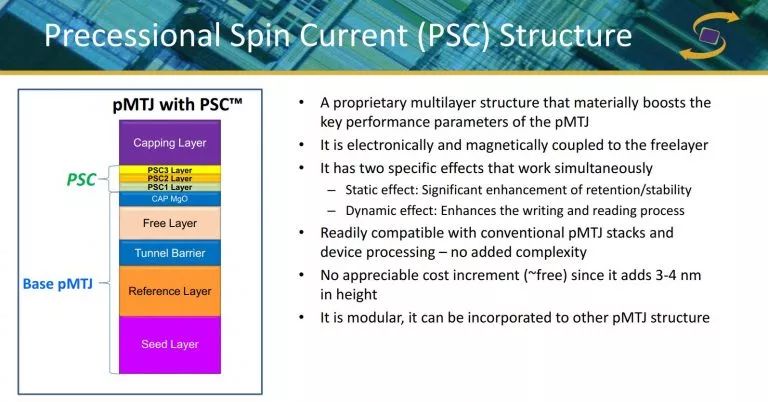

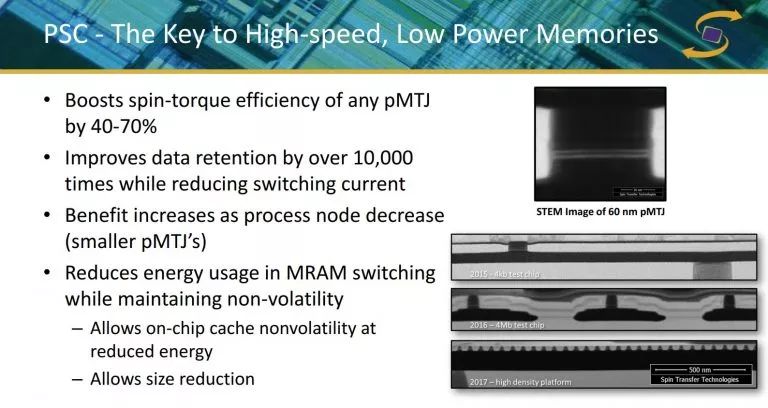

今天,STT宣布了新的突破,该公司称之为进动自旋电流(PSC)。STT声称,这种新方法有望将MRAM器件的自旋扭矩效率提高40%至70%,因而使保存时间比以前长10000倍。按照这种新方法,以前数据保存一小时,现在可以保存一年多,同时减小了写入电流。该公司是这样描述的:

PSC结构是一大突破,因为它实际上将决定数据保存的静态能量势垒(energy barrier)与控制开关电流的动态开关过程分离开来。因此,PSC结构添加到任何垂直磁性隧道结(pMTJ)后,获得的好处包括如下:

pMTJ没有电流流过时,会出现更高的能量势垒,这对于长时间保存数据而言再理想不过。

电流流过、器件正在写入新状态时,自旋极化效应加强,这对于尽量减小开关电流,并将器件寿命延长好多个数量级来说再理想不过。

PSC结构一开始就被设计成模块化,可以用任何pMTJ来制造:无论是该公司自己的pMTJ,还是其他来源的pMTJ。PSC结构是在pMTJ沉积过程中制造的,使pMTJ部件的高度增加了约4纳米。该结构与一系列广泛的标准MRAM制造工艺、材料和工具箱兼容,因而任何工厂都能轻松将PSC结构做入到现有的pMTJ部件中,并不显著增加复杂性或制造成本。

那么这可能如何影响未来处理器的设计呢?MRAM的一个优势是,你可以在与SRAM同样大小的空间塞入四五倍多的MRAM。虽然MRAM的性能特点不如SRAM那么诱人,但我们已经看到了特定的市场对替代存储器技术颇有兴趣,使用NAND闪存作为服务器RAM就是个佐证。在一些场景下,容量更大但速度慢得多的缓存可能比我们今天使用的现有系统有效得多,对于对延迟不是特别敏感的应用环境而言更是如此。比如说,大容量的片上MRAM高速缓存有望充当一种实用的方法:在不影响功率曲线或裸片尺寸的情况下,提高集成图形性能。

我们采访了STT,它告诉我们其近期计划是致力于取代SRAM,而不是取代DRAM,因为MRAM在现阶段天生与SRAM更匹配。该公司希望在今年下半年之前完成客户验证,并在2019年年中之前将产品推向市场。我们还不是很愿意认为这场比赛的天平完全倾向于MRAM,但AMD和英特尔等公司绝对在想方设法提高器件性能、降低功耗。随着新节点的价值随着时间的推移而下降,像MRAM这种替代技术带来的影响会相应增大。

相关阅读:

Linux 4.16 正式发布:不再支持 8 种 CPU 架构,内核减少了 450000 行代码 !

这个 CPU bug 的锅「Intel or 阿里云」谁背 ?

CPU 芯片漏洞第二季的预告片来了: Skyfall 和 Solace

Intel CPU 曝大 BUG:迫使重新设计 Linux 和 Windows

AI 的崛起标志着 CPU 在 IT 界唱主角的时代宣告结束