台积电研发副总裁黄汉森:2050年晶体管能做到0.1纳米,氢原子尺度!

新智元报道

新智元报道

来源:anandtech、cnet

编辑:小芹,大明

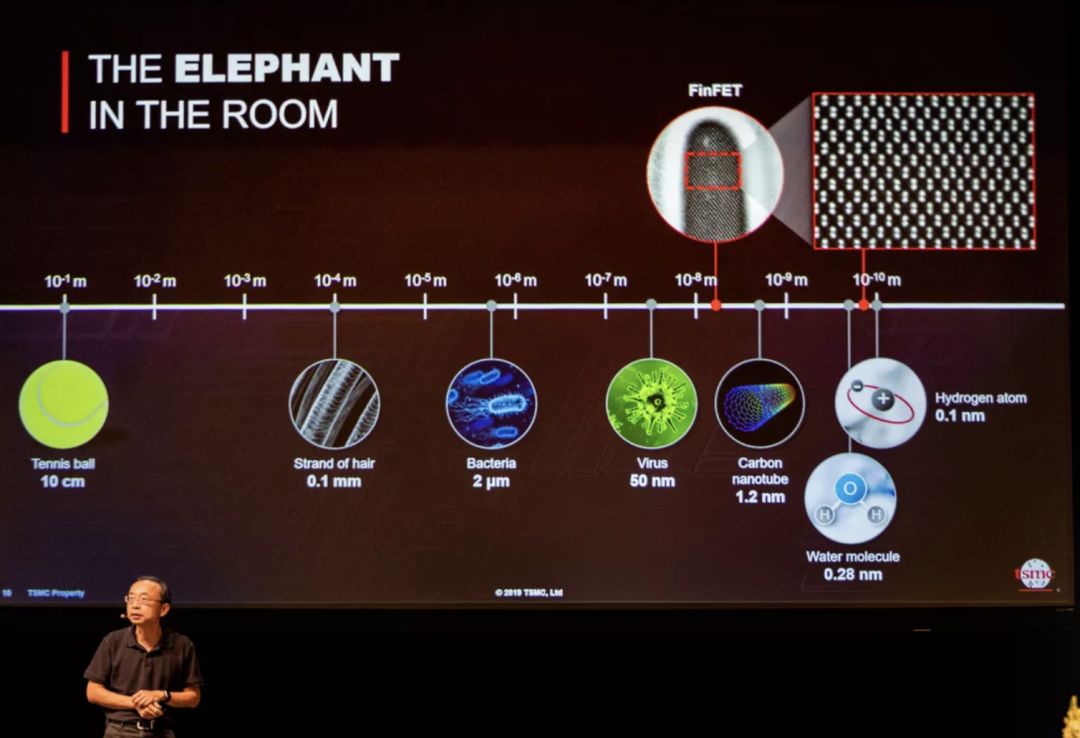

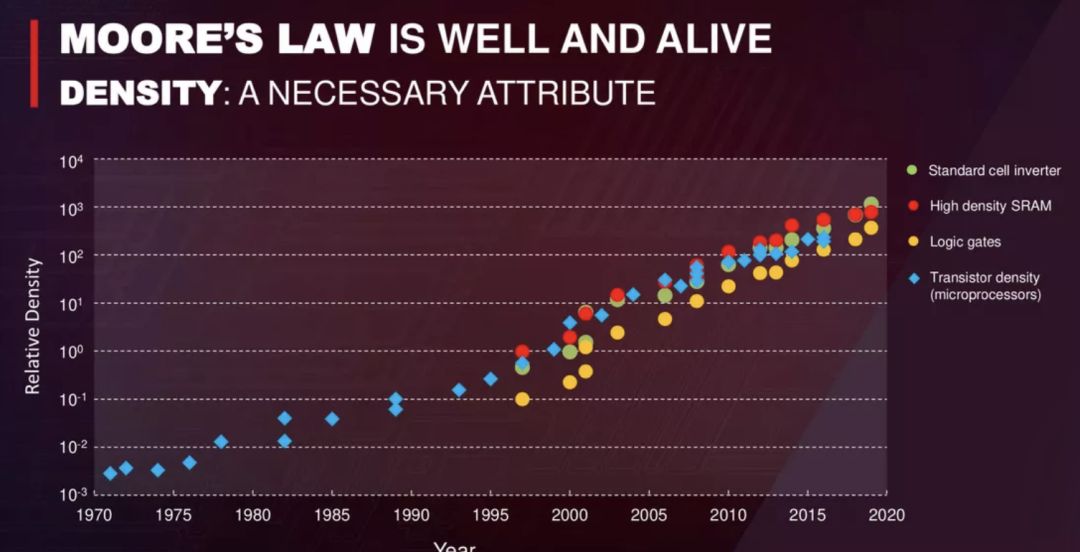

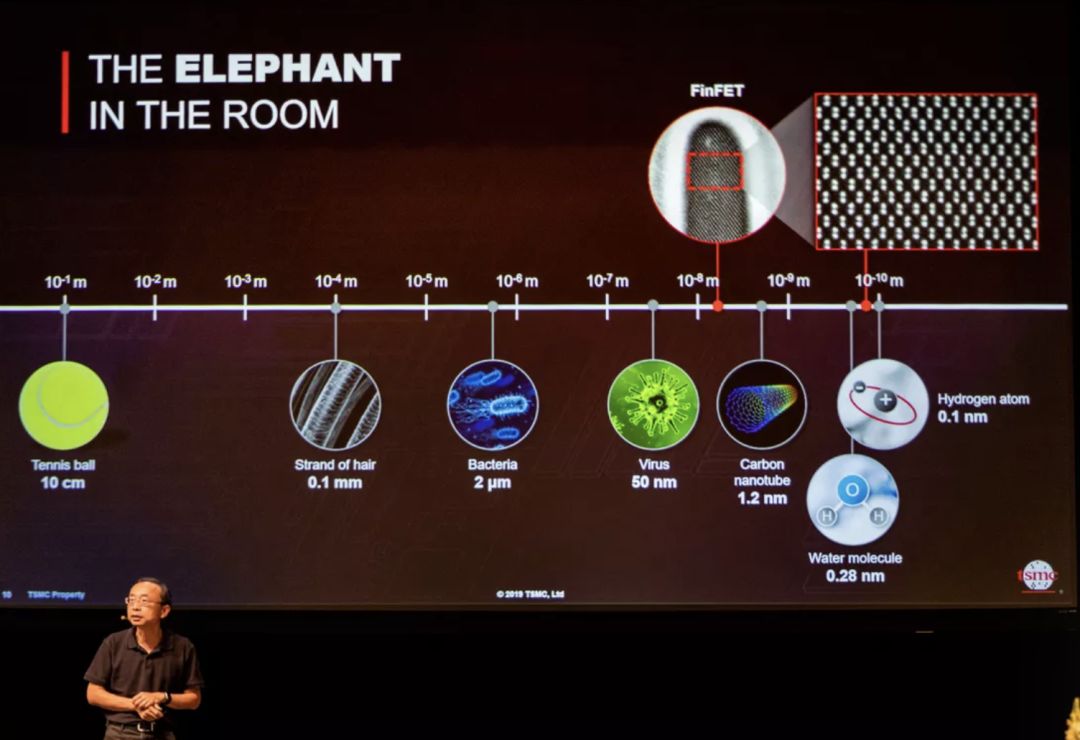

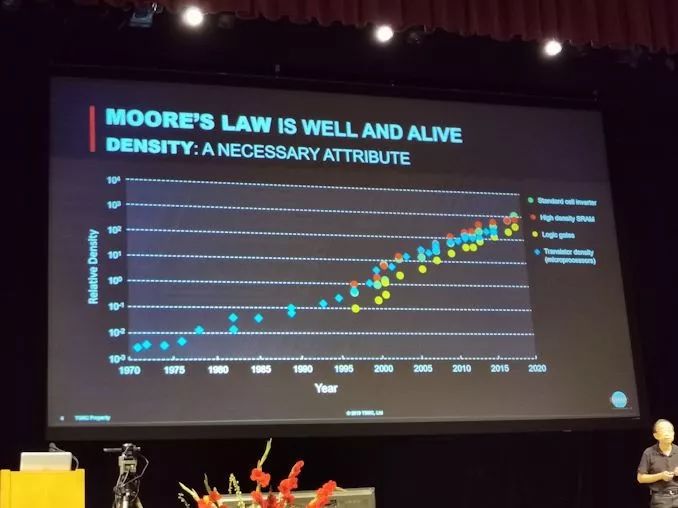

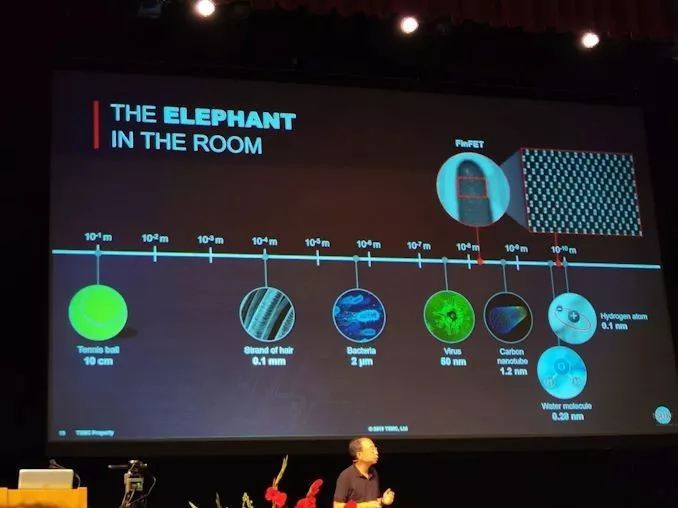

【新智元导读】台积电研发负责人Phillip Wong近日在硅谷举行的Hot Chips会议上表示,摩尔定律没死,依然有效且状况良好,并表示随着新技术的进步,到2050年晶体管做到0.1纳米,约等于氢原子的大小。

Philip Wong

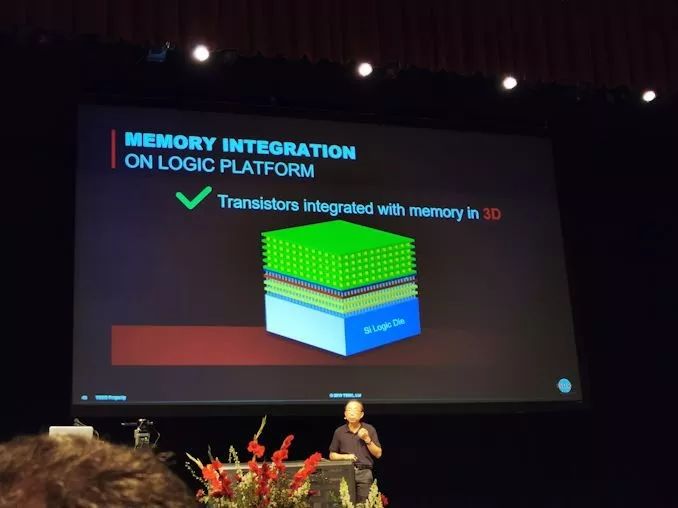

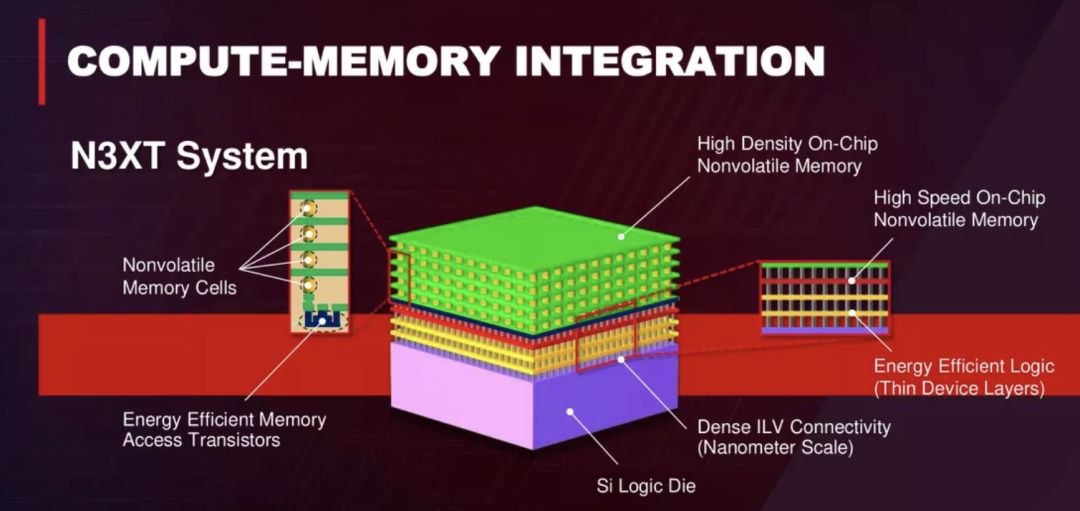

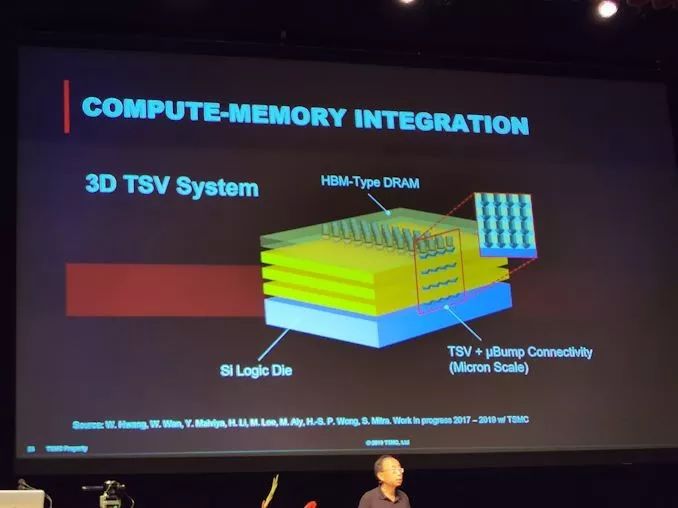

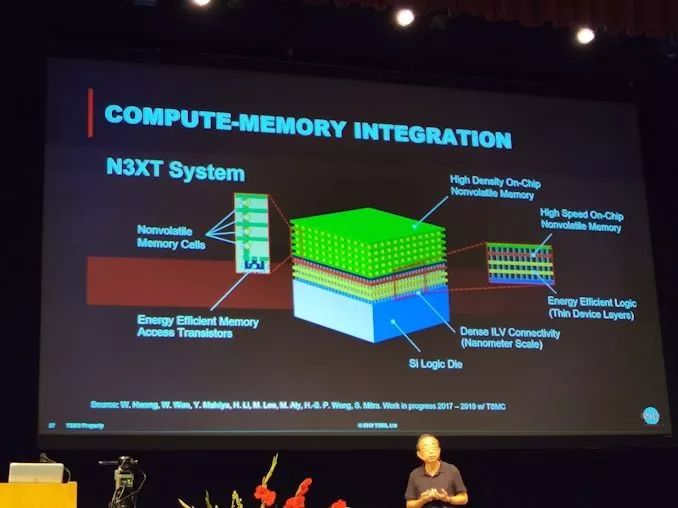

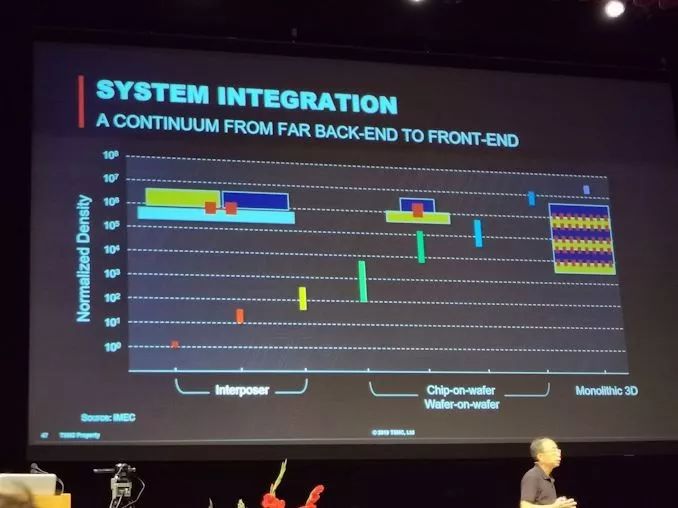

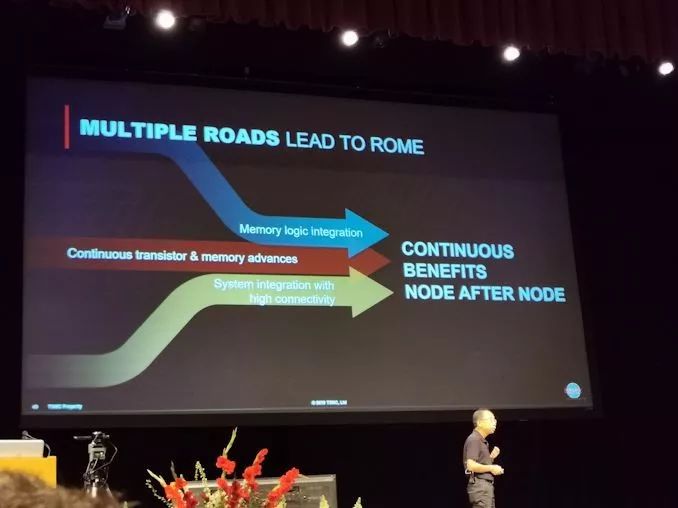

黄汉森预计,处理器将由不同芯片元件3D堆叠组成,而在当前这些元件通常是分开的。这将意味着芯片获得更小的尺寸和更高的性能。

新技术将使晶体管更快、更小。长期以来一直在考虑的一项技术——碳纳米管,现在正变得切实可行。另一种是被称为2D层状材料的材料,可以通过让电子更容易地流过芯片来提供类似的增强。

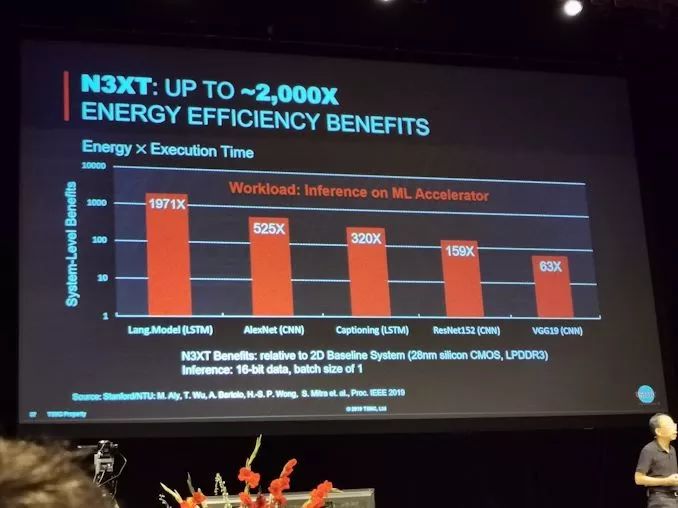

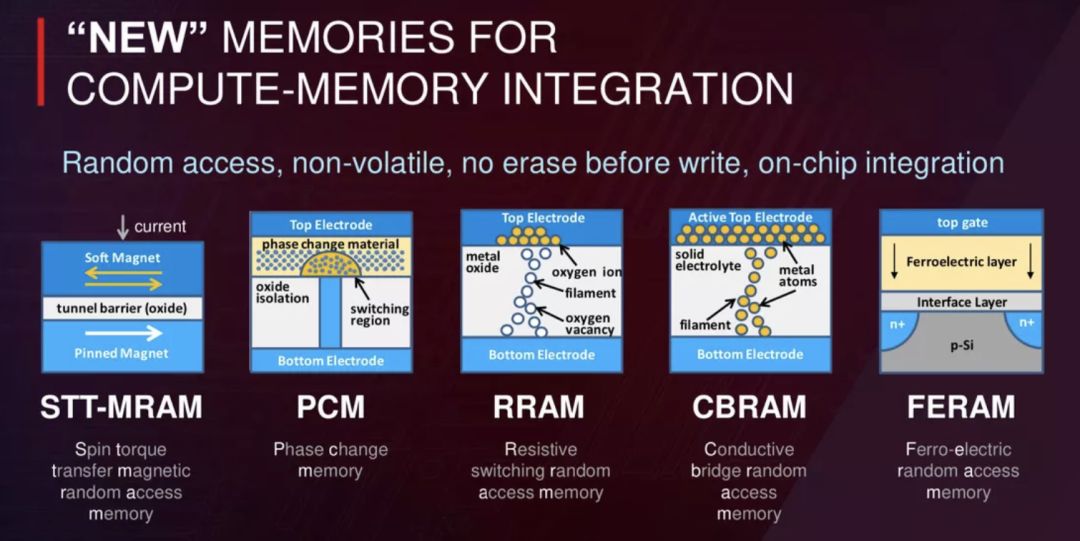

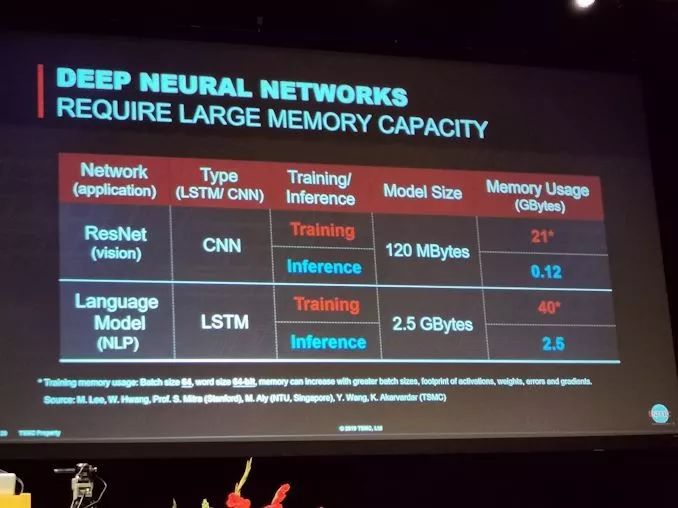

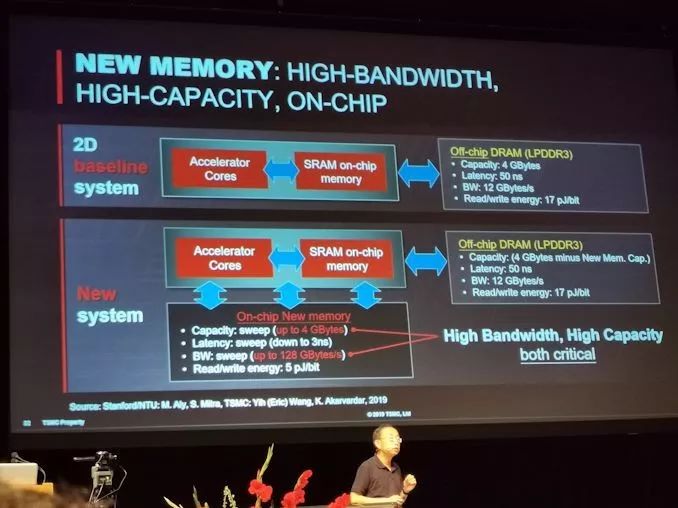

一些新的内存技术将直接构建到处理器中,而不是作为单独的芯片连接。这种快速连接将极大地提高性能,因为芯片上的逻辑电路(处理数据的部分)将更快地获得所需的数据,因此不必有太多闲置时间。

3D堆叠技术将意味着,如今孤立的计算机处理器功能可以被夹在多个层中,与高速数据通路相连。

登录查看更多

相关内容

HOT CHIPS:Hot Chips: A Symposium on High Performance Chips

Explanation:热门芯片:高性能芯片研讨会。

Publisher:IEEE。

SIT: http://www.hotchips.org/

Arxiv

9+阅读 · 2019年2月21日

Arxiv

3+阅读 · 2018年9月17日

Arxiv

7+阅读 · 2018年1月28日