Zen 5 架构将会获得全面的重新设计,并使用 3nm 工艺节点。

昨天,AMD 举行了 2022 Financial Analyst Day,在为投资者举行的活动上,公司分享了桌面、服务器、图形和移动方面产品的最新路线图。

作为助力 AMD 复苏并重新成为 x86 处理器领域有力竞争者的芯片架构,Zen 是 AMD 从最小嵌入式 CPU 到最大企业级芯片的基础。因此,未来几年在 Zen 架构上发生的事情对 AMD 乃至整个行业来说都是一件大事。

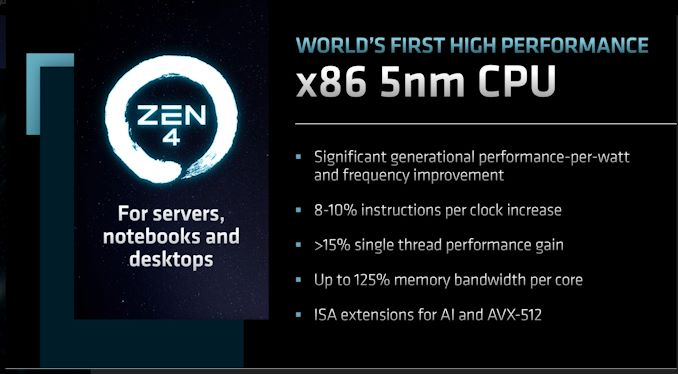

AMD 目前正在开发基于 Zen 4 架构的产品,这包括 Ryzen 7000(Raphael)消费级 CPU,以及第四代 EPYC(Genoa)服务器 CPU,这两款产品都将于今年晚些时候推出。

![]()

此前,我们已经看到了有关 Zen 4 的一些信息,最近一次官方发布是在 Computex 上发布 Ryzen 7000 的时候。Zen 4 带来了新的 CPU 小芯片核心以及新 I/O die,增加了对 PCI-E 5.0 和 DDR5 内存等新技术的支持。在性能方面,AMD 的目标是在其当前基于 Zen 3 的产品上显著提高每瓦性能和时钟速度。

在昨天的活动中,AMD 更新了很多细节,特别是有关每时钟指令速度(IPC)预期的问题。AMD 预计 Zen 4 将提供比 Zen 3 高 8-10% 的 IPC 提升。这和最初在 Computex 的 keynote 上暗示大部分性能收益来自时钟速度改进的情况大不一样。

AMD 还透露,他们预计下一代芯片的整体单线程性能提升 15% 以上——重点在于「以上」。单线程性能是 IPC 和时钟速度的结合,AMD 在这一点上不敢过于具体,因为他们还没有锁定最终的时钟速度。但正如我们在其 Computex 演示中看到的那样,目前在 Zen 4 桌面版上,对于轻线程工作负载,AMD 设定了高达 5.5GHz 的频率。

![]()

AMD 还确认了 Zen 4 的 AI 和 AVX-512 指令集架构(ISA)扩展,该公司没有说明这些扩展中的任何一个(或两者)是否会出现在所有 Zen 4 产品中,或者只是一个子集,但至少,有理由期待这些技术出现在 Zen 4 服务器版中。AI 指令的加入将有助于 AMD 在短期内跟上英特尔等其他竞争对手的步伐——最近一段时间,CPU AI 性能已经成为芯片制造商的必争之地。

AMD 将生产三种规格的 Zen 4 产品。这包括原版 Zen 4 内核,以及之前公布的 Zen 4c 内核:一个用于高密度服务器的紧凑型内核,将用于 128 核 EPYC Bergamo 处理器。AMD 还首次确认了 V-Cache 的 Zen 4 ——虽然是新信息,但鉴于 AMD 的 V-Cache 消费和服务器级部件的成功,这并不令人意外。

配备 3D V-Cache 的 Zen 3 内核已经与目前最高端的游戏 CPU Ryzen 7 5800X3D 和 Milan-X 处理器一起上市。这些芯片通过创新的复合链接工艺将一大块 SRAM 融合在计算芯片上。AMD 表示,3D V-Cache 芯片将成为其芯片系列中某些战略产品的固定配置。

有趣的是,AMD 正计划在 Zen 4 系列中同时使用 5nm 和 4nm 工艺。我们知道 Ryzen 7000 和 Genoa 将使用台积电 5nm 工艺,并且 Zen 4c 小芯片将构建在 N5 的 HPC 版本上。目前尚不清楚 AMD 在 4nm 上的路线图,但我们不能排除 AMD 对此预估较低,因为台积电 4nm 工艺是 5nm 的一个分支而非全新节点,最开始被归类为 5nm 变体。

![]()

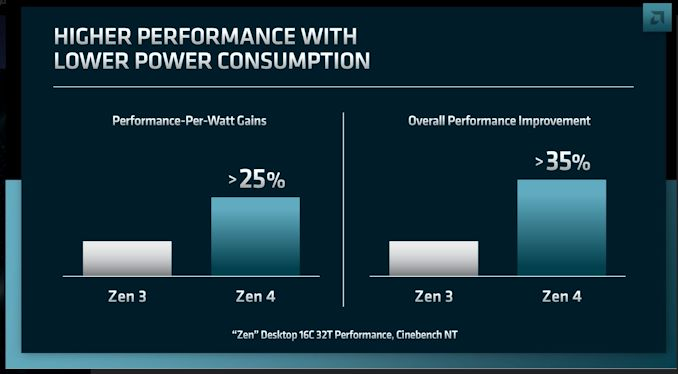

AMD 预计 Zen 4 的每瓦性能比 Zen 3 提高 25% 以上(基于运行 CineBench 的桌面 16 核芯片),同时整体性能提升超过 35%,这无疑是利用了架构单线程的更高性能和 AMD 先前披露的更高 TDP。这样看来提升非常可观。

![]()

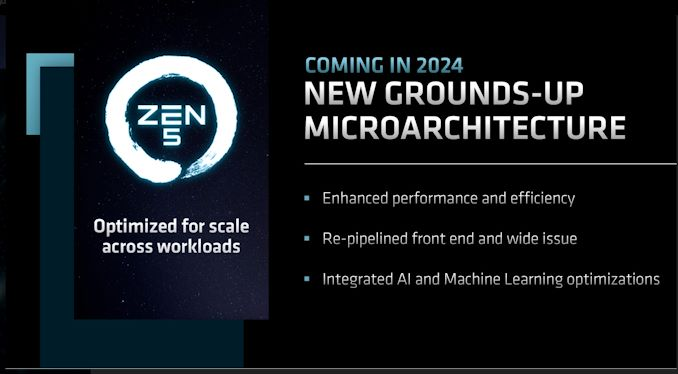

昨天,AMD 也公布了 Zen 5 架构的很多细节,该公司计划进行一些激进的更新。Zen 5 被称为「全新的微架构」,不仅仅是对 Zen 4 的增量改进。

根据 AMD 现在披露的内容,Zen 5 将重新对前端进行流水线化,并再次增加它们的发射宽度(issue width)。同时,在 Zen 4 的新 AI 指令基础之上,Zen 5 会集成更多 AI 和机器学习优化能力。AMD 目前已经有一个庞大的工具库,涵盖从人工智能指令到更多数据类型支持等内容。

AMD 预计 Zen 5 芯片堆栈与 Zen 4 相似——也就是说,它们将拥有相同的三重设计:原始 Zen 5 内核、紧凑型内核(Zen 5c)和 V-Cache 核心。对于 AMD 的客户来说,这种连续性非常重要,因为可以保证很多多定制配置在 2024 年前后的时间范围内继续可用。

![]()

AMD 同样计划在 Zen 5 上使用两个制程,Zen 5 CPU 内核将采用 4nm 和 3nm 工艺混合制造,与 Zen 4 的 5nm/4nm 混合不同,台积电的 4nm 和 3nm 节点大不相同。4nm 是 5nm 的优化版本,而 3nm 是一个全新的节点。因此如果 AMD 按照目前的规划推进,Zen 5 将跨越一个主要节点。

![]()

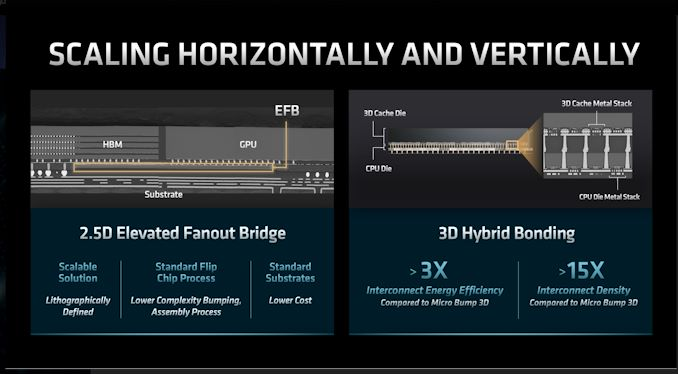

最后,AMD 还希望扩展小芯片连接的内容:其提出的 Infinity 互连将小芯片、内存和 I/O 芯片连接在一起获得了很大成功,AMD 甚至已在使用它来连接加速器,如 GPU,用于数据中心应用程序。

现在,AMD 计划扩大范围并添加支持其最近收购的 Xilinx IP 的扩展,AMD 还将支持来自第三方供应商的 IP,从而使其能够获得更低的通信延迟。

https://www.anandtech.com/show/17439/amd-zen-architecture-roadmap-zen-5-in-2024-with-allnew-microarchitecture

https://www.tomshardware.com/news/amd-shares-new-cpu-core-roadmap-3nm-zen-5-by-2024-4th-gen-infinity-architecture

![]()

© THE END

转载请联系本公众号获得授权

投稿或寻求报道:content@jiqizhixin.com