本综述全面梳理了生成式 AI(Generative AI)与智能体 AI(Agentic AI)在数字电子设计自动化(EDA)领域的深度融合。论文首先回顾了 EDA 领域的范式演进:从传统的计算机辅助设计(CAD)过渡到 AI 辅助 EDA(AI4EDA),并最终迈向新兴的 AI 原生(AI-Native)及智能体(Agentic)设计范式。 我们详述了这些范式在数字芯片设计全流程中的应用,具体包括:基于多模态基础模型构建智能体认知架构、前端 RTL 代码生成与智能验证,以及融合算法创新与工具编排(Tool Orchestration)的后端物理设计。通过综合案例研究,我们验证了上述方法论,展示了从微架构定义到 GDSII 的全流程实际可行性。本文特别强调了“跨阶段反馈回路”的潜力,即智能体能够利用后端的 PPA(功耗、性能、面积)指标自主优化前端逻辑。

此外,本综述深入探讨了该技术对安全性的双重影响,涵盖新型对抗性风险、自动化漏洞修复以及隐私保护基础设施。最后,文章批判性地总结了当前面临的幻觉(Hallucinations)、数据稀缺及“黑盒”工具等挑战,并勾勒了迈向 L4 级自主芯片设计的未来趋势。本工作旨在定义新兴的智能体 EDA(Agentic EDA)领域,并为从 AI 辅助工具向全自主“设计工程师”的转型提供战略路线图。

1 引言:范式重构

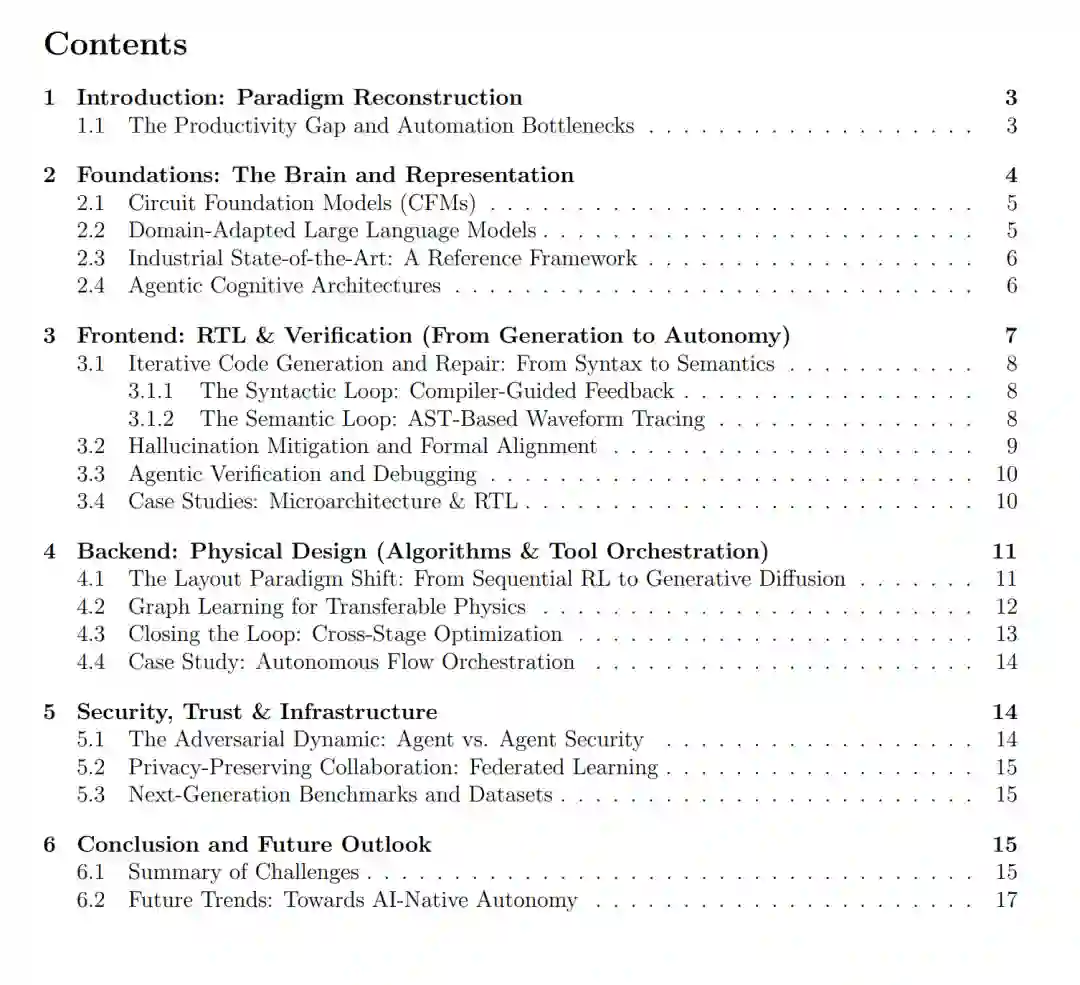

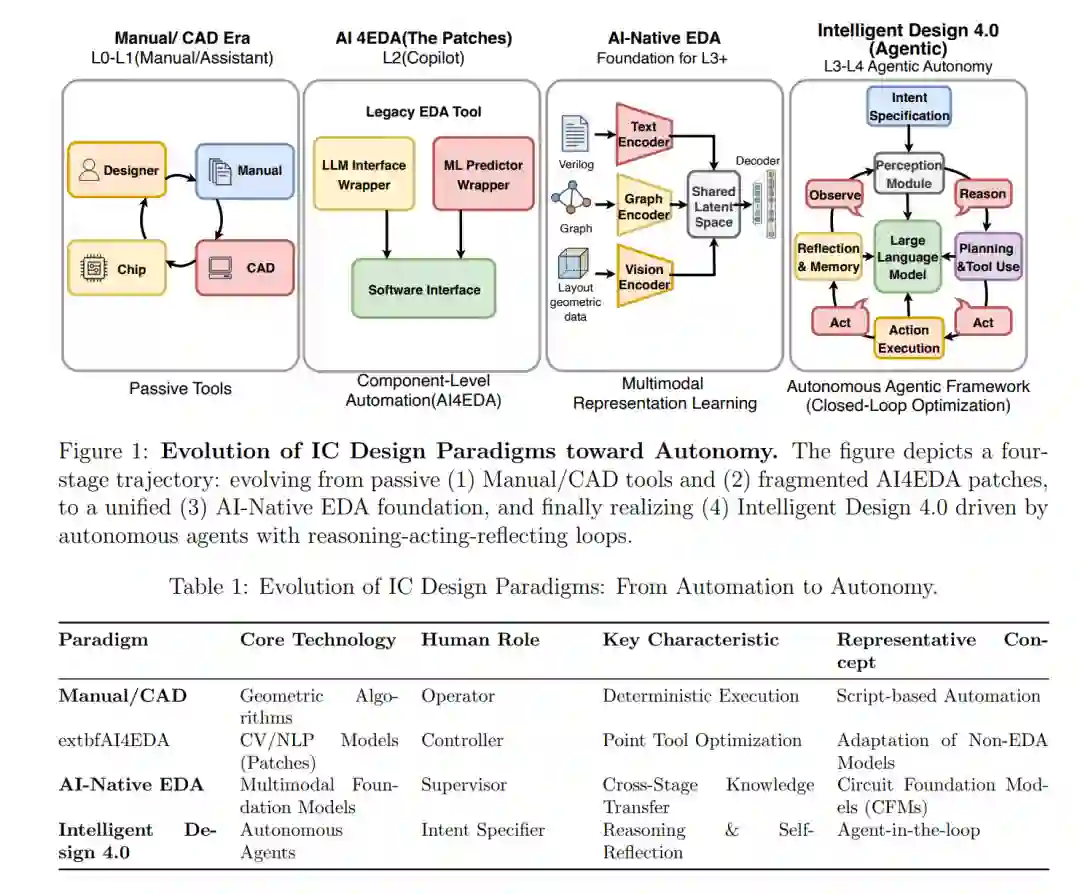

集成电路(IC)设计行业正处于一个历史性的转折点。几十年来,电子设计自动化(EDA)经历了从手动布局到计算机辅助设计(CAD),再到针对特定逻辑综合与物理设计任务的算法驱动自动化的线性演进。尽管近年来机器学习已被引入以增强特定的点工具(Point Tools),但大语言模型(LLMs)与智能体 AI(Agentic AI)的爆发式出现,标志着从“自动化辅助”向“自主设计”的深刻转变 [1]。如图 1 所示,这一演进路径预示着设计系统将超越静态优化算法,向具备推理、规划和工具编排(Tool Orchestration)能力的认知系统跨越。

**1.1 生产力差距与自动化瓶颈

摩尔定律下的复杂度爆炸。 尽管摩尔定律的边际效益面临物理缩放挑战,但现代片上系统(SoC)的规模已攀升至数千亿个晶体管。然而,人类的设计生产力未能跟上这种复杂度的增长,从而产生了关键的“生产力差距”。经验数据表明,仅验证任务就往往消耗整个开发周期的 60% 到 70%,而设计成本随工艺节点的进步而剧增 [2]。传统的基于脚本的自动化已日益不足以弥合这一差距,这使得我们在演进时间轴后期所示的范式转变成为必然。 从 AI4EDA 到 AI 原生 EDA(AI-Native EDA)。 近年来,学术界和工业界广泛探索了“AI 赋能 EDA”(AI4EDA)。然而,Chen 等人 [3] 认为,目前的 AI4EDA 方法大多只是将计算机视觉(CV)或自然语言处理(NLP)的模型迁移至电路任务。如图 1 中的阶段 2 所示(通常对应 L2 级 Copilot 系统),这些方法往往只是现有软件接口上的“补丁”,而非底层的重构。这与张等人 [4] 提出的“第三代 AI”愿景相契合,即强调知识、数据与推理的融合——这是本综述所探讨的自主智能体的前提条件。 术语与自主等级。 为了保持各章节术语的一致性,我们参照表 6 总结的分类法,将自主等级分为 L0-L5。简言之,L2 对应“Copilot”式辅助,而 L3+ 则指代具备多步执行回路、可在减少人工干预的情况下运行的智能体系统。 相比之下,“AI 原生 EDA”(图 1 中的阶段 3,支持 L3 级智能体工作流)已成为必然的演进方向。它倡导将 AI 置于设计流程的核心,依托于能够同时理解网表、寄存器传输级(RTL)代码和物理布局的多模态电路基础模型(CFMs) [3, 5]。 与前序工作的关系。 本综述直接建立在 Chen 等人 [3] 确立的“AI 原生 EDA”愿景之上。尽管其工作奠定了基础设施基础——提出将电路基础模型(CFMs)作为统一表示——但本文重点关注认知执行层。我们探讨了智能体工作流如何超越这一基础,从静态感知转向动态自主行动,有效地实现从“大脑”(模型)到“工程师”(智能体)的进化。

智能设计 4.0:从工具到智能体。 必须在传统自动化与新兴的自主性之间划出明确的界限。早期的 EDA 工具,即使是经过机器学习增强的工具(阶段 2),其功能本质上仍属于自动化(Automation):它们是确定性的点解决方案,本质上需要“人机耦合”(human-in-the-loop)来桥接断开的任务。相比之下,智能设计 4.0 代表了自主性(Autonomy):智能体能够感知全局流程语境、规划多步策略并进行自我修正,将人类的角色转变为监督性的“人机监护”(on-the-loop)。 更尖锐地讲:传统的 AI 优化的是“扳手”(工具),而智能体 AI 旨在实现使用扳手的“工程师”的自动化。如图 1 最终阶段所示,这些配备了“推理-行动-反思”回路(Reasoning-Acting-Reflecting loop)的自主智能体可以解析模糊的意图,编排复杂的工具链,并从执行日志中学习以迭代优化设计。

革命还是炒作? 尽管愿景宏大,但大模型在硬件设计中的应用仍面临严峻挑战,包括幻觉(Hallucinations)、数据稀缺以及 EDA 工具作为黑盒的不透明性。He 等人 [6] 对 LLM 在代码生成、验证和优化方面的表现进行了批判性评估,指出虽然进展令人振奋,但距离实现愿景中真正的工业级“自动驾驶”仍有显著差距。此外,Xu 等人 [2] 强调,业界必须超越表面的指标,建立专注于端到端 PPA(功耗、性能、面积)的严谨基准测试,以确定这一技术转变是否代表了一场真正的革命。

本综述的范围。 鉴于数字电路与模拟电路在设计范式上的根本差异——前者严重依赖逻辑综合和离散优化,而后者依赖连续的物理方程——本综述明确聚焦于数字芯片设计。我们探讨了智能体工作流如何改变标准的 RTL-to-GDSII 流程,而将模拟电路自动化的独特挑战留给未来的专门综述。